Principle of 8051 MCU: A Comprehensive Guide to Its Architecture and Applications

Introduction

The 8051 microcontroller stands as a cornerstone in the world of embedded systems, representing one of the most influential and enduring architectures in computing history. Since its introduction by Intel in 1980, the 8051 has evolved from a simple microcontroller to a family of devices powering countless applications across industries. Its longevity—spanning over four decades—speaks volumes about its robust design, versatility, and adaptability to changing technological landscapes. The fundamental principles behind the 8051 MCU have become so ingrained in embedded systems education that they serve as the introductory platform for countless engineers worldwide.

What makes the 8051 particularly remarkable is its perfect balance of simplicity and capability. While modern microcontrollers offer significantly more processing power and features, the 8051’s straightforward architecture provides an ideal framework for understanding microcontroller fundamentals without overwhelming complexity. This accessibility, combined with its real-world utility, has cemented its place in both educational curricula and commercial products. From automotive systems to consumer electronics, industrial automation to Internet of Things devices, the 8051 continues to find new applications, demonstrating the timelessness of its core design principles.

The purpose of this comprehensive guide is to explore the architectural foundation of the 8051 microcontroller, examining its core components, instruction set, and programming model in detail. By understanding these fundamental principles, developers can not only work effectively with 8051-based systems but also gain insights that transfer to more complex microcontroller architectures. Whether you’re a student encountering microcontrollers for the first time or an experienced engineer refreshing foundational knowledge, grasping the principles of the 8051 MCU provides valuable perspective on embedded systems design that remains relevant despite technological advancements.

Architectural Foundation of 8051 Microcontroller

Core Components and Block Diagram

At its heart, the 8051 microcontroller architecture represents a sophisticated integration of computational, memory, and peripheral elements designed to work in harmony. The central processing unit (CPU) serves as the brain of the system, coordinating all operations through an 8-bit ALU (Arithmetic Logic Unit) that can perform basic arithmetic operations including addition, subtraction, multiplication, and division, as well as logical operations like AND, OR, and XOR. The CPU operates based on a clock signal that determines the speed of instruction execution, with original 8051 variants typically running at 12 MHz, resulting in most instructions executing in 1-2 microseconds.

The memory organization of the 8051 follows a Harvard architecture pattern, featuring separate address spaces for program memory (ROM) and data memory (RAM). This separation allows simultaneous access to instructions and data, potentially improving performance over von Neumann architectures where both share the same bus. The standard 8051 configuration includes 4KB of ROM (often implemented as EPROM or Flash in modern variants) for program storage and 128 bytes of RAM for data storage, though many contemporary 8051 derivatives offer significantly expanded memory capacities. Special Function Registers (SFRs) occupy a distinct address space from 128 to 255 and provide control and data access to all the microcontroller’s peripherals and core functions.

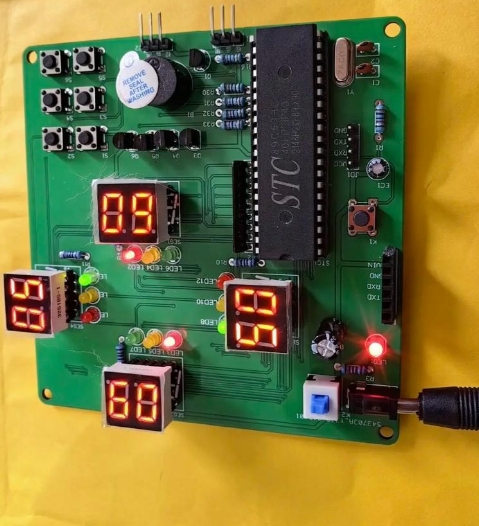

A critical aspect of the 8051’s enduring success lies in its comprehensive peripheral integration. Beyond the core computational elements, the architecture incorporates multiple built-in peripherals that reduce external component requirements in embedded designs. These include: - Four 8-bit bidirectional I/O ports (P0, P1, P2, P3) providing up to 32 general-purpose digital I/O lines - Two 16-bit timer/counters (Timer 0 and Timer 1) capable of operating as timers (counting machine cycles) or event counters - A full-duplex UART (Universal Asynchronous Receiver/Transmitter) for serial communication - An interrupt controller with five interrupt sources (two external, two timer-based, and one serial) - Oscillator and clock circuitry requiring only an external crystal to establish the operating frequency - Boolean processor allowing single-bit operations on directly addressable bits

This high level of integration made the 8051 revolutionary at its introduction, as it significantly reduced the component count and board space required for embedded control applications compared to multi-chip solutions prevalent at the time.

Memory Organization and Addressing Modes

The memory architecture of the 8051 employs a sophisticated scheme that efficiently manages different types of memory within the constraints of an 8-bit address bus. Program Memory (ROM) begins at address 0000H and extends up to FFFFH in modern variants, though the original specification supported only up to 0FFFH (4KB). The lower portion of this memory contains special reserved areas, most notably the reset vector at 0000H where execution begins after reset, and interrupt service routine vectors spaced every 8 bytes from 0003H to 0023H. This arrangement allows each interrupt source to jump to its respective service routine without complex vectoring logic.

Internal Data Memory (RAM) represents one of the most distinctive features of the 8051 architecture, organized into multiple overlapping regions that serve different purposes. The first 128 bytes (00H to 7FH) comprise the main RAM area, with the lowest 32 bytes (00H to 1FH) organized as four register banks of eight registers each (R0-R7). The active register bank is selected through bits in the Program Status Word (PSW), enabling fast context switching—a valuable feature for interrupt service routines. The next 16 bytes (20H to 2FH) form a bit-addressable area where each of the 128 bits can be directly manipulated using the 8051’s powerful bit-processing instructions, providing efficient control of individual I/O lines and status flags.

The addressing modes available in the 8051 instruction set provide flexibility in accessing different memory spaces and peripherals: - Immediate addressing where the operand value is included directly in the instruction - Direct addressing allowing access to any location in the lower 128 bytes of RAM or SFRs using an 8-bit address - Register indirect addressing using registers R0 or R1 as pointers to RAM locations - Register addressing where the operand is in one of the eight working registers (R0-R7) - Indexed addressing used primarily for reading program memory tables using the DPTR or PC as base register and accumulator as offset

This variety of addressing modes enables efficient code generation across different application scenarios, from mathematical computations requiring immediate values to data processing applications needing flexible memory access patterns.

Special Function Registers and Their Roles

Special Function Registers (SFRs) form the control nexus of the 8051 microcontroller, providing the interface between software and hardware peripherals. Located in address space 80H through FFH, these registers are directly accessible using direct addressing mode and include all the critical control and status registers for the microcontroller’s operation. Some SFRs are both readable and writable, allowing configuration and monitoring of peripheral status, while others may be read-only or write-only depending on their specific function. The SFR space is not fully populated in standard 8051 implementations, with specific addresses reserved for particular functions.

Among the most critical SFRs is the Accumulator (ACC), which serves as the primary register for arithmetic and logical operations, data transfers, and I/O operations. Many instructions implicitly use the accumulator, making it the most frequently accessed register in the architecture. The B Register works alongside the accumulator for multiplication and division operations but can also serve as a general-purpose scratchpad register for other operations. The Program Status Word (PSW) contains essential status flags including Carry (CY), Auxiliary Carry (AC), Overflow (OV), and Parity (P), along with register bank selection bits (RS0 and RS1) that determine which of the four register banks is currently active.

Other vital SFRs include: - Stack Pointer (SP) which points to the last used location in the software stack - Data Pointer (DPTR) comprising two registers (DPL and DPH) that form a 16-bit pointer primarily used for accessing external memory - Power Control Register (PCON) containing power management bits including those for activating idle and power-down modes - Timer Mode Register (TMOD) and Timer Control Register (TCON) which configure and control timer/counter operations - Serial Control Register (SCON) managing serial communication parameters and status - Interrupt Enable (IE) and Interrupt Priority (IP) registers controlling interrupt system configuration

Understanding these SFRs is essential for effective 8051 programming, as they provide direct control over all aspects of microcontroller operation from basic computation to peripheral management.

Instruction Set and Programming Model

Classification of Instructions

The 8051 instruction set comprises 255 opcodes implementing 111 distinct instructions that can be broadly categorized based on their functional purpose. Arithmetic instructions include addition (ADD, ADDC), subtraction (SUBB), multiplication (MUL), division (DIV), increment (INC), and decrement (DEC) operations that primarily work with the accumulator and other operands. Logical instructions perform bitwise operations including AND, OR, XOR, complement, rotate, and swap operations on data in various memory locations. Both arithmetic and logical instructions automatically update relevant flags in the PSW, enabling subsequent conditional operations based on computation results.

Data transfer instructions facilitate movement of data between different memory spaces and registers within the microcontroller architecture. The MOV instruction provides flexible data transfer capabilities between any two operands without affecting flags in the PSW. Specialized data transfer instructions include MOVX for accessing external data memory using either DPTR or R0/R1 as pointers, and MOVC for reading program memory tables—a capability frequently used for lookup tables in mathematical functions or character generation. Stack operations PUSH and POP allow temporary storage and retrieval of data from the software stack managed by the SP register.

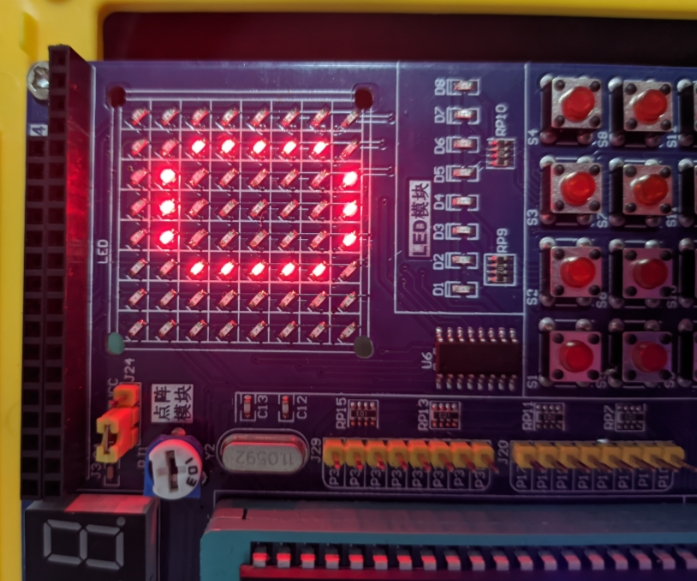

Boolean or bit-level instructions represent one of the most powerful features unique to the 8051 architecture among contemporary microcontrollers. These instructions allow direct manipulation of individual bits in both the bit-addressable RAM area (20H-2FH) and certain SFRs without requiring read-modify-write sequences common in other architectures. The comprehensive set includes bit set (SETB), bit clear (CLR), bit complement (CPL), along with bit-based jump instructions that test individual bits for conditional branching. This capability makes the 8051 exceptionally efficient for control applications requiring manipulation of individual I/O lines or status flags.

Addressing Modes in Detail

The efficiency of any microcontroller heavily depends on its ability to access operands flexibly, and the addressing modes available in the 8051 provide comprehensive coverage of common programming needs. Immediate addressing (#data) incorporates constant values directly within instructions—for example, MOV A,#25H loads hexadecimal value 25 immediately into the accumulator. This mode provides fast access to constants but makes values fixed at compile time. Direct addressing uses an 8-bit address to access any location in lower RAM (00H-7FH) or SFRs (80H-FFH), enabling efficient access to frequently used variables without intermediate register loading.

Register indirect addressing utilizes R0 or R1 as pointers to RAM locations (@R0 or @R1), providing limited but efficient memory indexing capabilities within internal RAM. This mode proves particularly valuable for implementing arrays, buffers, and data structures where sequential access patterns dominate. Indexed addressing combines a base register (either DPTR or PC) with an offset in the accumulator to form a complete address—primarily used with MOVC instructions for reading lookup tables from program memory. This powerful mode enables efficient implementation of jump tables, character generators, and mathematical function approximations.

The combination of these addressing modes creates a balanced system that supports various programming paradigms while maintaining reasonable instruction encoding efficiency. Programmers can select appropriate addressing modes based on access frequency—using direct addressing for frequently accessed variables while employing register indirect addressing for array processing tasks. This flexibility contributes significantly to code density advantages that have historically made compiled 8051 code relatively compact compared to other contemporary architectures—an important consideration in embedded systems where memory constraints often dictate solution feasibility.

Programming Techniques and Optimization

Effective 8051 programming requires understanding not just instruction syntax but also architectural characteristics that influence performance optimization strategies. Given Harvard architecture limitations preventing self-modifying code common in von Neumann systems; programmers must employ alternative techniques like lookup tables when dynamic code generation would otherwise be used. Careful register bank selection minimizes push/pop overhead during interrupt servicing—critical for time-sensitive applications where interrupt latency directly impacts system responsiveness.

Memory optimization represents another crucial consideration given typical resource constraints in embedded systems targeting cost-sensitive applications judicious variable placement across different memory spaces significantly impacts performance internal RAM delivers fastest access but remains limited external RAM offers expanded capacity slower access times compiler directives typically control allocation but understanding implications enables manual optimization critical code sections resource management becomes particularly important large data structures buffer management careful planning prevents memory fragmentation inefficient utilization common beginners especially those transitioning higher level languages accustomed abundant resources automatic management typical modern computing environments

Interrupt handling demands careful planning maximize reliability minimize latency proper interrupt service routine design requires minimal necessary processing deferred main loop possible preserving stack space reducing worst case execution time interrupt driven architectures particularly benefit boolean processing capabilities individual flag management eliminating polling loops reducing processor overhead power consumption especially important battery powered applications combination these techniques enables creation efficient responsive embedded systems despite relatively modest raw processing capabilities original architecture modern derivatives often incorporate enhanced features reduced power consumption increased clock speeds maintaining backward compatibility proven instruction set

Applications and Modern Relevance

Traditional Application Domains

Despite its age; the principle of 8051 MCU continues finding relevance numerous application domains particularly cost sensitive high volume products automotive industry represents significant application area where various electronic control units ECUs implement using variants body electronics including power window controls seat positioning systems climate control interfaces simple sensor data acquisition systems industrial automation another major domain programmable logic controllers PLCs especially lower end models frequently employ cores peripheral functions motor control systems often utilize capabilities precise timing pulse generation measurement consumer electronics perhaps most visible application area remote controls television audio systems kitchen appliances toys countless other devices benefit combination adequate performance extreme cost effectiveness

The educational sector maintains strong interest architecture serves ideal teaching platform microcontroller concepts straightforward easily understood architecture provides complete feature set demonstrating fundamental principles without overwhelming complexity students countless universities technical schools worldwide continue introducing embedded systems programming through laboratories courses based variants development tools compilers debuggers remain widely available affordable lowering barriers entry aspiring engineers hobbyists open source community developed numerous toolchains hardware platforms based cores further extending accessibility knowledge resources available self directed learning

Legacy system maintenance represents another area continued relevance countless installed systems industrial commercial medical applications continue operating based original derivatives replacement often proves economically unjustified when functioning adequately instead organizations maintain upgrade existing systems requiring continued expertise development supporting these platforms specialized engineering firms focus exclusively maintaining extending legacy systems particular expertise rare valuable skill set certain industries manufacturing facilities may run equipment decades requiring specialized knowledge support

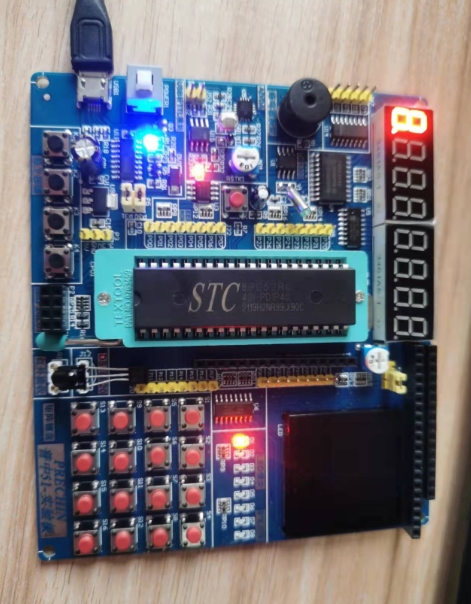

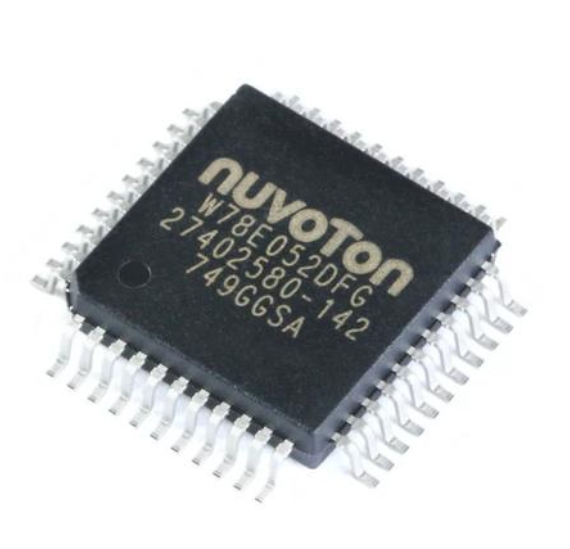

Modern Derivatives and Enhancements

Contemporary semiconductor manufacturers have extensively evolved core maintaining backward compatibility while addressing limitations original design modern derivatives typically feature significantly enhanced capabilities including expanded memory sizes flash program memory reaching kilobytes random access memory measuring kilobytes increased clock speeds operating frequencies exceeding hundred megahertz reduced power consumption operating voltages lowered volt ranges making suitable battery powered IoT devices additional peripherals analog digital converters multiple serial interfaces including SPI I²C CAN USB controllers pulse width modulation outputs sophisticated timer structures watchdog timers brown out detection**

These enhancements maintain relevance rapidly evolving technology landscape particularly Internet Things applications where cost power consumption often trump raw processing requirements many connected devices require modest computational resources primarily managing sensor data communication protocols well suited these tasks manufacturers like Silicon Laboratories NXP Microchip Atmel continue introducing new variants targeting specific market segments demonstrating enduring viability underlying architectural principles specialized versions featuring radio interfaces encryption accelerators ultra low power operation enable secure energy efficient connected devices competitive against modern architectures specific application areas**

Software tool support remains robust with modern development environments offering sophisticated debugging profiling optimization capabilities even higher level language support through C compilers with efficient code generation several manufacturers provide free development tools lowering barrier entry new projects open source community maintains various toolchains hardware abstraction layers enabling portable code across different vendor implementations this extensive ecosystem support ensures new development continues despite architecture maturity availability royalty free intellectual property cores further encourages incorporation custom system chip designs**

Future Outlook and ICGOODFIND Resources

The future appears surprisingly bright given longevity demonstrated resilience adaptation changing technological requirements several factors suggest continued relevance foreseeable future enormous installed base ensures demand maintenance enhancement existing systems extensive developer familiarity reduces training costs compared newer architectures extremely competitive manufacturing costs make compelling choice price sensitive applications proven reliability critical systems where failure not option educational value introducing fundamental concepts ensures continued pipeline new engineers familiar architecture**

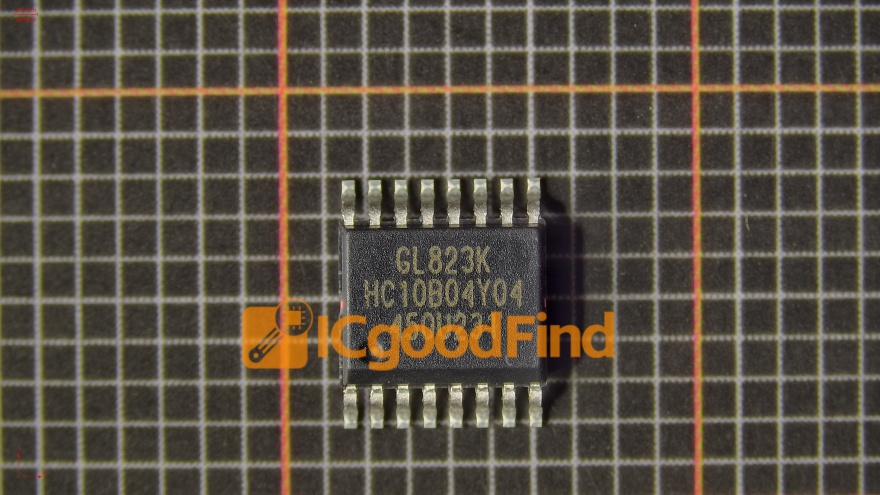

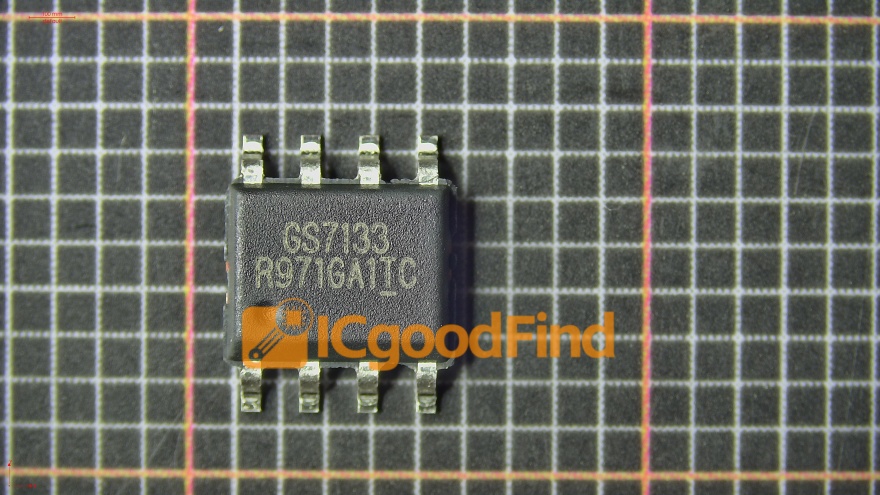

For developers seeking comprehensive resources about modern implementations applications; platforms like ICGOODFIND offer valuable curated information component selection application notes reference designs ICGOODFIND particularly useful identifying appropriate variants specific project requirements comparing features across different manufacturers accessing technical documentation quickly efficiently platform aggregates information multiple sources saving research time providing centralized starting point development projects their systematic organization technical specifications simplifies initial component selection process especially valuable engineers evaluating multiple options constrained timelines**

As technology continues evolving likely see further specialization targeting emerging application areas while maintaining compatibility proven foundation represents remarkable example engineering design standing test time adaptability demonstrates value solid fundamental principles properly implemented continuing provide foundation innovation decades come whether working legacy system designing new product learning embedded systems fundamentals understanding principles provides valuable perspective transcends specific implementation details**

Conclusion

The enduring legacy demonstrates how well conceived architectural principles can transcend specific technological implementations create lasting impact entire industry fields simple yet effective design struck balance capability accessibility rarely achieved computing history continues serving vital role both education industry testament original designers vision flexibility allowed successive generations engineers build upon foundation creating enhanced versions meeting evolving requirements while maintaining conceptual continuity**

From humble beginnings single Intel product grown extensive family devices manufactured countless companies worldwide serving diverse applications automotive industrial consumer medical sectors core architectural principles remain recognizable despite numerous enhancements expansions modern variants fundamental understanding provides framework comprehending more complex microcontroller architectures making valuable starting point anyone pursuing embedded systems development career**

As move increasingly connected world seemingly simple architectures find renewed purpose constrained devices forming edge network internet things where cost power efficiency reliability often outweigh raw processing requirements combination modern enhancements proven foundation ensures continued relevance years come platforms ICGOODFIND help navigate landscape variants identify optimal solutions specific project requirements preserving knowledge resources ensures future generations can continue learning applying these timeless embedded systems principles.