The MCS-51 Microcontroller: An Enduring Legacy in Embedded Systems

Introduction

The world of embedded systems is built upon a foundation of pioneering technologies, and few have left as indelible a mark as the MCS-51 microcontroller family. Often referred to simply as the 8051, this iconic 8-bit microcontroller architecture has demonstrated remarkable longevity since its introduction by Intel in 1980. What began as Intel’s solution for embedded control applications has evolved into one of the most successful microcontroller architectures in history, with countless variants produced by numerous manufacturers worldwide. The MCS-51’s enduring relevance stems from its elegant simplicity, robust architecture, and extensive ecosystem that continues to support both legacy systems and new developments. This article explores the technical foundations, evolutionary journey, and contemporary applications of this remarkable microcontroller family that continues to power innovation across industries decades after its creation.

The Architectural Foundation of MCS-51

Core Architecture and Memory Organization

The MCS-51 architecture established a blueprint that would influence microcontroller design for generations. At its heart lies an 8-bit CPU optimized for control applications rather than raw computational power. The processor features a rich instruction set with 111 instructions, including extensive bit-level operations that proved exceptionally useful for controlling individual I/O pins—a fundamental requirement in embedded systems. The architecture employs a Harvard memory architecture with separate address spaces for program and data memory, enabling simultaneous access and improving performance for real-time control applications.

Memory organization in the standard MCS-51 follows a distinctive pattern that became familiar to generations of embedded developers. The original architecture supported up to 64KB of external program memory (ROM) and 64KB of external data memory (RAM), while incorporating 4KB of on-chip ROM and 128 bytes of on-chip RAM. This internal RAM includes both general-purpose registers and specially allocated bit-addressable memory space—a feature that significantly simplified programming for control applications where individual bits often needed to be set or cleared to control hardware. The stack resides within this internal RAM and grows upward, limited to 256 bytes in the original implementation.

Peripheral Integration and I/O Capabilities

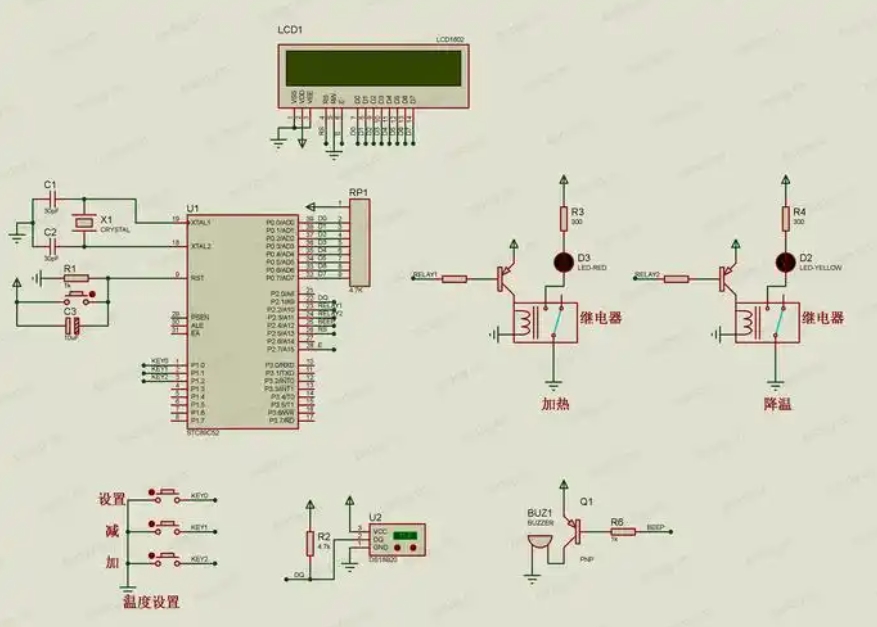

One of the MCS-51’s most significant contributions was establishing the model of a complete system on a chip, integrating not just the processor core but essential peripherals that reduced component count in embedded designs. Standard features included four 8-bit bidirectional I/O ports, providing 32 general-purpose digital I/O lines that could interface directly with external devices. These ports could source and sink significant current compared to modern microcontrollers, often eliminating the need for external drivers in many applications.

The integrated serial communication capability represented another forward-thinking feature of the MCS-51 architecture. The Universal Asynchronous Receiver/Transmitter (UART) enabled communication with PCs, other microcontrollers, and various peripheral chips—a capability that became increasingly important as systems grew more interconnected. Additionally, the architecture included two 16-bit timer/counters that could be configured for various timing, counting, and pulse-width measurement tasks. Many variants later expanded these capabilities with additional timers, enhanced UARTs, and specialized communication controllers like SPI and I2C, further cementing the architecture’s versatility.

Interrupt System and Power Management

The interrupt handling system of the MCS-51 established patterns still seen in modern microcontrollers. The architecture supported five interrupt sources in its original implementation: two external interrupts, two timer interrupts, and one serial port interrupt. Each could be individually enabled or disabled through dedicated interrupt enable registers, with configurable priority levels determining servicing order when multiple interrupts occurred simultaneously. This flexible interrupt structure enabled responsive real-time control—a critical requirement for the embedded applications the MCS-51 was designed to serve.

Power management capabilities, though primitive by today’s standards, were innovative for their time. The architecture included idle and power-down modes that could significantly reduce power consumption during periods of inactivity—an important consideration for battery-powered applications. In power-down mode, the processor core would halt while RAM contents were preserved, consuming minimal current until an external interrupt or hardware reset restored normal operation. These features demonstrated the forward-thinking design philosophy that would contribute to the architecture’s longevity.

Evolution and Variants of the M51 Architecture

Manufacturer Expansion and Architectural Licensing

Intel’s decision to license the MCS-51 architecture proved pivotal in its widespread adoption and evolution. Numerous semiconductor manufacturers developed their own compatible variants, each adding unique features while maintaining instruction-set compatibility. Companies like Philips (now NXP Semiconductors), Atmel (now Microchip), Siemens, Dallas Semiconductor, and many others produced enhanced versions with additional peripherals, more memory, improved performance, and lower power consumption. This competitive ecosystem drove innovation while preserving software compatibility, creating a virtuous cycle of improvement and adoption.

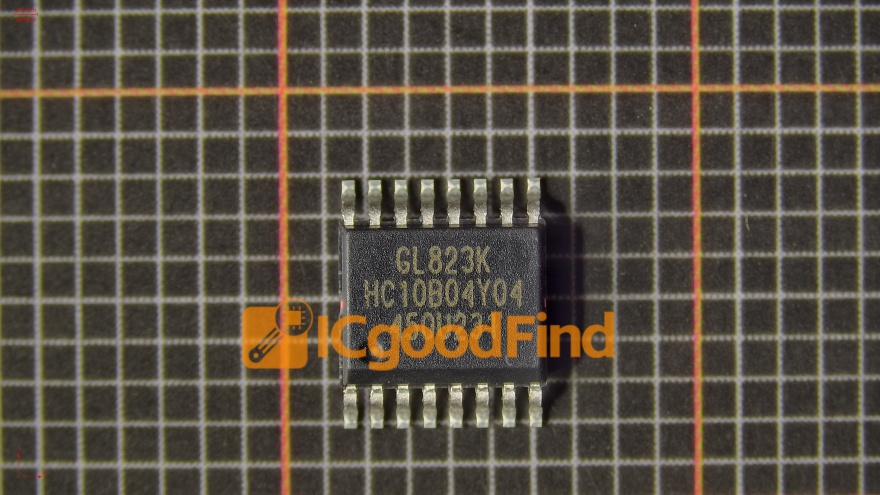

The architectural enhancements introduced by various manufacturers addressed specific application needs while maintaining backward compatibility. Philips focused on industrial applications, introducing variants with enhanced I²C capabilities, more timers, and analog peripherals. Atmel revolutionized the ecosystem with Flash memory-based versions that dramatically simplified development and field updates. Dallas Semiconductor produced high-speed variants with extended temperature ranges for demanding environments. ICGOODFIND has documented hundreds of these variants, providing engineers with valuable comparative data for component selection.

Technological Advancements and Performance Scaling

Clock speed evolution demonstrates the remarkable scalability of the MCS-51 architecture. While original implementations typically operated at 12MHz, modern derivatives routinely achieve clock frequencies exceeding 100MHz while maintaining full compatibility. This performance scaling has been achieved through architectural enhancements like single-cycle execution (versus the original 12-clock machine cycle), pipelined instruction processing, and improved semiconductor processes. Some manufacturers have even developed 16-bit and 32-bit cores that maintain object-code compatibility with the original 8-bit instruction set—a testament to the soundness of the initial architectural decisions.

Memory capacity expansion represents another significant evolutionary path. From the original 4KB ROM/128B RAM configuration, modern variants now offer Flash program memory ranging from 1KB to 512KB or more, with RAM expanding proportionally to support increasingly complex applications. Some manufacturers have even incorporated external memory interfaces that maintain the familiar MCS-51 bus structure while supporting modern memory technologies. This backward-compatible scaling has enabled applications to grow in complexity without requiring complete redesigns or retraining of engineering teams.

Specialized Derivatives and Application-Specific Variants

The MCS-51 architecture has proven remarkably adaptable to specialized application domains through targeted enhancements. USB-enabled variants emerged as universal serial bus became ubiquitous, integrating USB controllers alongside the traditional MCS-51 core. Similarly, CAN bus variants addressed automotive and industrial networking requirements while maintaining software compatibility with existing code bases. Wireless connectivity has been incorporated through variants with integrated RF transceivers or dedicated communication coprocessors.

Application-specific standard products (ASSPs) based on the MCS-51 core have targeted vertical markets including motor control, power management, touch sensing, and automotive systems. These devices package specialized peripherals—such as high-resolution PWMs, analog comparators, dedicated cryptographic engines, or LCD controllers—around the familiar CPU core, reducing development time for target applications. The persistence of these application-specific variants decades after the architecture’s introduction demonstrates its continued relevance in an era of increasingly specialized semiconductor solutions.

Modern Applications and Development Ecosystem

Contemporary Application Domains

Industrial automation and control systems continue to leverage MCS-51 compatible microcontrollers due to their proven reliability, deterministic operation, and extensive existing code bases. In manufacturing environments where equipment lifetimes span decades, the ability to maintain component compatibility while incrementally enhancing functionality provides significant economic advantages. Modern MCS-51 variants with enhanced analog capabilities, robust communication interfaces, and extended temperature ranges remain competitive solutions for many industrial control applications.

Consumer electronics represents another domain where MCS-51 derivatives maintain significant presence. From kitchen appliances to power tools, toy products to remote controls, the cost-effective combination of adequate performance, low power consumption, and extensive development resources makes these microcontrollers attractive for high-volume applications. Modern ultra-low-power variants have found particular success in battery-operated devices where energy efficiency trumps raw computational performance.

Development Tools and Software Ecosystem

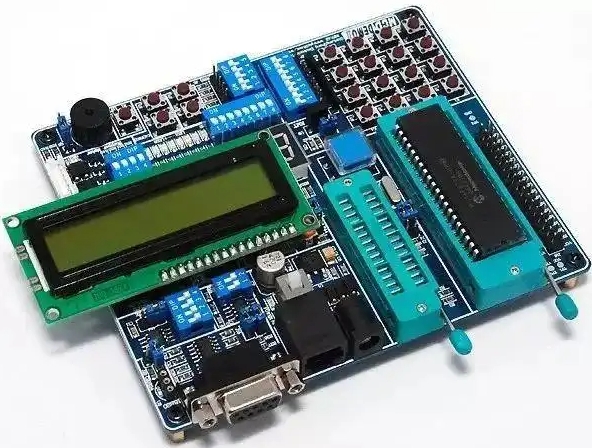

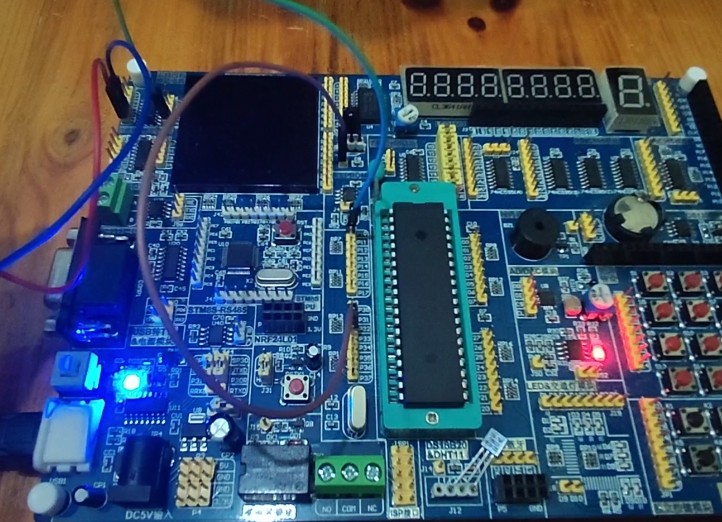

The maturity of the MCS-51 development ecosystem represents one of its strongest competitive advantages. Developers can choose from multiple mature C compilers that efficiently target the architecture, along with sophisticated debuggers, simulators, and integrated development environments. The availability of proven real-time operating systems (RTOS) simplifies development of complex applications while maintaining the reliability expected from embedded control systems.

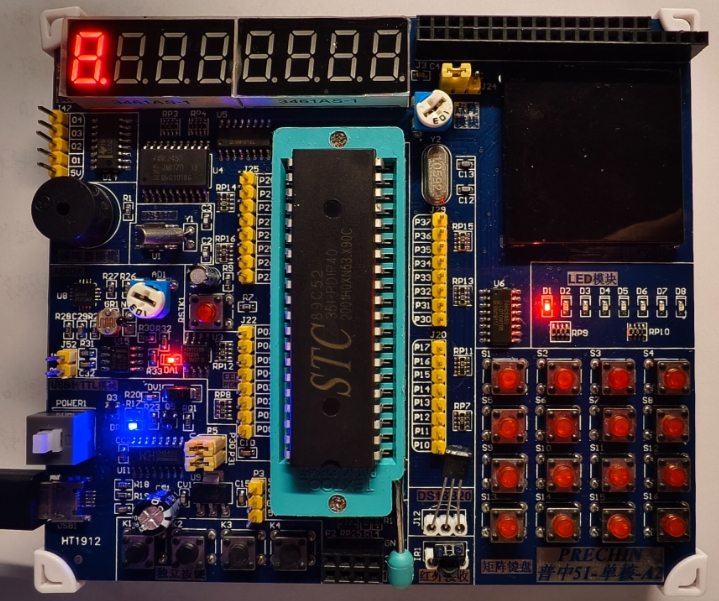

Educational institutions worldwide continue to introduce students to embedded systems using MCS-51 compatible microcontrollers due to their straightforward architecture, excellent documentation, and low-cost development tools. This continuous influx of newly trained engineers ensures ongoing familiarity with the architecture while supporting its ecosystem of tools and libraries. Online resources ranging from manufacturer documentation to community forums provide extensive support for both novice and experienced developers.

Legacy System Support and Future Prospects

The critical role of MCS-51 compatibles in supporting legacy systems cannot be overstated. Industrial equipment, medical devices, automotive subsystems, and aerospace applications designed decades ago continue to operate reliably with original components or form-fit-function replacements. Semiconductor manufacturers recognize this ongoing requirement and continue producing compatible devices even as they develop more modern architectures—sometimes including MCS-51 cores as peripheral controllers within more complex system-on-chip designs.

Looking toward the future, the MCS-51 architecture continues to evolve rather than fade into obsolescence. Modern implementations focus on reducing power consumption further, integrating more advanced analog peripherals, and enhancing security features while maintaining compatibility. The rise of IoT edge devices has created new opportunities for ultra-low-power variants with integrated wireless capabilities. ICGOODFIND’s market analysis suggests continued design wins for MCS-51 compatible devices in cost-sensitive applications where reliability and time-to-market outweigh raw computational requirements.

Conclusion

The MCS-51 microcontroller family represents a remarkable success story in the history of computing technology—an architecture that has remained relevant across five decades of rapid technological change. Its enduring appeal stems from a powerful combination of technical merit,

economic factors,

and ecosystem support.

The elegant simplicity of its design,

the robustness of its implementation,

and the flexibility demonstrated through countless variants have created a lasting legacy that continues to influence embedded systems development.

From its origins as Intel’s embedded control solution to its current status as a widely licensed,

pervasively deployed architecture,

the MCS-51 has proven uniquely adaptable to changing technological landscapes.

While newer architectures offer superior computational performance for increasingly complex applications,

the MCS-51 maintains strong positions in markets where reliability,

cost-effectiveness,

and development efficiency outweigh raw processing power.

Its continued evolution ensures this pioneering architecture will remain part of the embedded systems landscape for years to come,

powering everything from simple consumer devices to critical industrial systems with the same dependable efficiency that has characterized its impressive history.