Mastering MCU Interrupt Programming: A Guide to Efficient Embedded Systems

Introduction

In the realm of embedded systems, the Microcontroller Unit (MCU) serves as the brain, executing instructions and managing peripherals. However, a fundamental challenge arises: how can an MCU efficiently handle multiple, often unpredictable, events without constantly polling its inputs and wasting precious processing cycles? The answer lies in a powerful architectural feature—interrupts. MCU interrupt programming is not merely a technical skill; it is the cornerstone of creating responsive, efficient, and real-time capable embedded applications. From a simple button press to complex communication protocols, interrupts allow the main program flow to be “interrupted” to handle urgent tasks immediately, ensuring timely responses and optimal resource utilization. This article delves deep into the principles, implementation, and best practices of interrupt programming, a critical competency for any embedded systems engineer.

The Core Principles of MCU Interrupts

At its heart, an interrupt is a signal sent to the MCU’s core processor, requesting immediate attention. Think of it as a doorbell ring while you’re working; you pause your current task, address the visitor, and then seamlessly return to where you left off. This mechanism is far superior to polling, where the CPU repeatedly checks the status of a device, leading to inefficient CPU usage.

The process follows a strict sequence managed by hardware and software: 1. Interrupt Request (IRQ): An event (e.g., timer overflow, data received on UART, pin state change) triggers an interrupt request. 2. Context Saving: The processor automatically saves its current state (program counter, status register) onto the stack. 3. Jump to ISR: The CPU jumps to a predefined memory location—the Interrupt Service Routine (ISR)—which is a function containing the code to handle the event. 4. ISR Execution: The ISR executes. A critical rule here is that ISRs should be as short and fast as possible. Lengthy operations can block other interrupts and degrade system responsiveness. 5. Context Restoration & Return: Upon completion, the processor restores the saved context from the stack and resumes the main program exactly where it left off.

A key concept in interrupt management is priority. Most modern MCUs allow interrupts to be assigned priority levels. A higher-priority interrupt can, in turn, interrupt a lower-priority ISR, a scenario known as nested interrupts. Proper priority assignment is crucial for designing deterministic systems where the most critical events are guaranteed a response.

Furthermore, interrupts can be broadly categorized. Hardware interrupts are generated by external pins or internal peripherals like timers and ADCs. Software interrupts are triggered explicitly by software instructions. Understanding the MCU’s interrupt vector table—a map linking each interrupt source to its corresponding ISR address—is the first step in practical implementation.

Implementing Interrupts: A Practical Framework

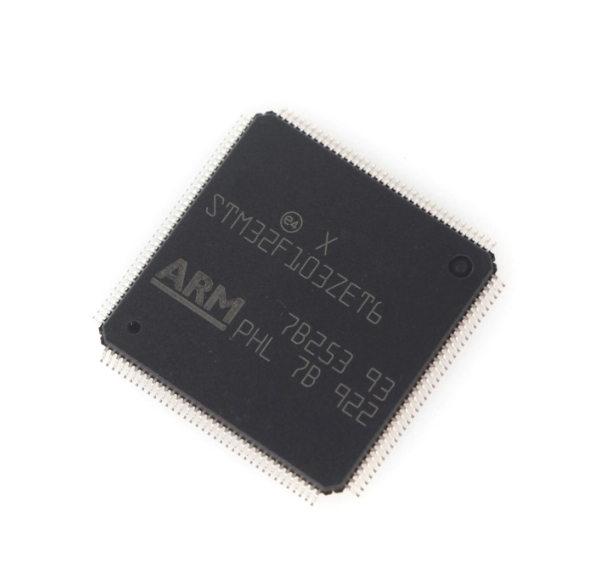

Moving from theory to practice involves several concrete steps that vary slightly between MCU architectures (e.g., ARM Cortex-M, AVR, PIC) but follow a universal pattern.

1. Configuration of the Peripheral and Interrupt Controller: Before an interrupt can occur, the source must be enabled and configured. This typically involves: * Peripheral Setup: Configuring the specific module (e.g., a timer for overflow mode, a UART for receive-complete mode). * Global Interrupt Enable: Often a master switch in the processor status register (e.g., the I bit in AVR, PRIMASK in Cortex-M). * Peripheral Interrupt Enable: Enabling the interrupt generation feature within the peripheral’s control register. * Priority Setting (if available): Assigning a priority level in the Nested Vectored Interrupt Controller (NVIC) for ARM-based chips.

2. Writing the Interrupt Service Routine (ISR): The ISR is a special function with specific syntax defined by the compiler and MCU. It must be declared correctly so the compiler places its address in the correct spot in the vector table.

// Example for an AVR Timer0 overflow ISR

ISR(TIMER0_OVF_vect) {

// Clear the interrupt flag (often done automatically or manually)

// Perform minimal necessary tasks:

// e.g., increment a counter, toggle a flag.

}

The golden rule for ISRs is minimalism. They should not use long loops, blocking calls, or heavy computations. A common design pattern is for the ISR to only set a flag or push data into a buffer, letting the main loop handle processing later.

3. Managing Shared Data and Race Conditions: This is one of the most critical and error-prone aspects of interrupt programming. Since both the ISR and the main program can access global variables (e.g., counters, buffers), corruption can occur if an interrupt happens midway through a non-atomic main program operation. * Use of Volatile Keyword: All global variables accessed within an ISR must be declared as volatile (e.g., volatile uint8_t data_ready = 0;). This instructs the compiler not to optimize away reads or writes to this variable, ensuring it always fetches its value from memory. * Critical Sections: Code in the main program that accesses shared data must be protected. This is often done by temporarily disabling interrupts before accessing the data and re-enabling them afterward.

// In main program

cli(); // Disable global interrupts (AVR)

my_shared_variable = new_value; // Safe critical operation

sei(); // Re-enable global interrupts

For more advanced MCUs, atomic operations or mutexes might be available.

Advanced Considerations and Best Practices

Mastering basic interrupts is just the beginning. Robust system design requires navigating advanced topics.

Interrupt Latency and Performance: Latency is the time delay between the interrupt request and the start of ISR execution. It’s influenced by factors like maximum interrupt disable times in code, hardware response time, and whether other higher-priority interrupts are running. Profiling and minimizing latency is essential for hard real-time systems. Tools like logic analyzers and debuggers are invaluable here.

Common Pitfalls to Avoid: * Forgetting to Clear Interrupt Flags: If the flag that triggered the interrupt isn’t cleared inside the ISR, the MCU will immediately re-enter the ISR upon exit, causing an infinite loop. * Writing Blocking ISRs: Performing delays (_delay_ms()), waiting for peripherals inside an ISR, or printing via slow serial links can cripple system performance. * Stack Overflow: Deeply nested interrupts or large local variables inside ISRs can cause stack overflow and catastrophic system failure. Ensuring adequate stack size is crucial. * Resource Starvation: If interrupts fire too frequently, the main loop may never get CPU time—a condition known as livelock.

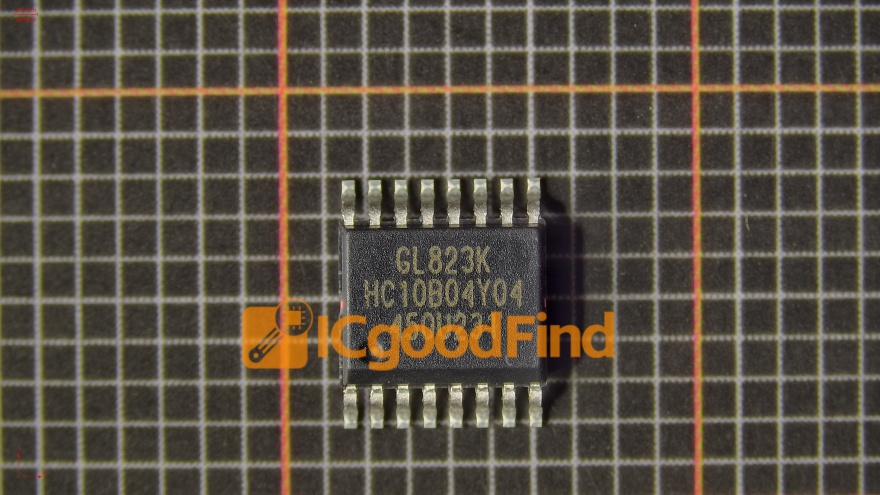

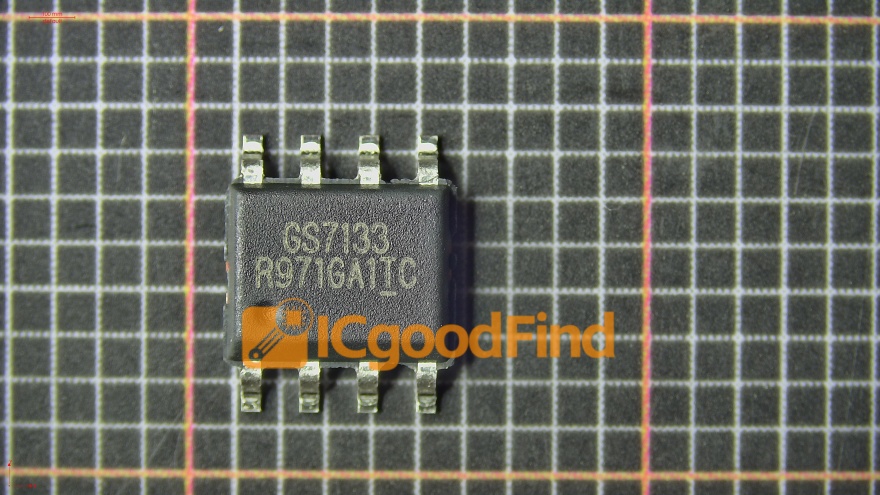

For engineers seeking to deepen their expertise beyond foundational tutorials and vendor datasheets, finding curated, high-quality resources on advanced topics like DMA with interrupts, low-power sleep modes with wake-up interrupts, or real-time operating system (RTOS) context switching can be challenging. This is where specialized platforms prove their value. For instance, developers looking for comprehensive tutorials, component comparisons, or community-vetted best practices for complex embedded topics might find relevant resources on platforms like ICGOODFIND, which aggregates technical information that can streamline project development.

Conclusion

MCU interrupt programming transforms an embedded system from a simple sequential executor into a dynamic, responsive entity capable of handling real-world asynchronous events. It demands a disciplined approach—from understanding hardware vector tables and writing lean ISRs to meticulously managing shared resources and system timing. While challenging due to its asynchronous and often non-deterministic debugging nature, proficiency with interrupts separates novice programmers from expert embedded systems architects. By adhering to best practices such as minimizing ISR workload, protecting shared data with volatile and critical sections, and rigorously profiling system latency, developers can harness their full power. As systems grow more complex with multiple sensors and communication protocols, mastering interrupts—supported by continuous learning from quality engineering resources—remains an indispensable skill for building efficient and reliable embedded solutions.