Mastering MCU Interrupts: The Key to Responsive and Efficient Embedded Systems

Introduction

In the intricate world of embedded systems, where microcontrollers (MCUs) serve as the silent brains behind countless devices, achieving real-time responsiveness and efficient power management is paramount. At the heart of this capability lies a fundamental concept: the MCU interrupt. Unlike simple polling loops that constantly check for events, interrupts provide a sophisticated mechanism for an MCU to respond immediately to internal or external triggers, pausing its current task to handle a higher-priority event. This article delves deep into the architecture, types, and best practices of MCU interrupts, exploring how they form the backbone of responsive systems from smart home gadgets to automotive control units. Mastering interrupts is not just a programming skill; it’s essential for designing systems that are both powerful and efficient.

The Core Architecture and Mechanism of Interrupts

An interrupt is essentially a signal that alerts the processor to a high-priority event requiring immediate attention. When an interrupt occurs, the MCU performs a critical sequence of actions known as the interrupt service routine (ISR) handling flow.

First, the processor completes the current instruction it is executing. This ensures architectural state consistency. Then, it automatically saves the current context—crucial registers like the program counter and status register—onto the stack. This preservation is vital for seamlessly resuming the original task later. The processor then fetches the address of the corresponding ISR from a special table in memory called the interrupt vector table (IVT). Each interrupt source has a predefined slot in this table. Execution jumps to the ISR, where the specific event (e.g., a key press, data received, timer overflow) is handled. A well-designed ISR is characteristically short and fast, performing only the minimum necessary work, such as setting a flag or moving data. Finally, upon completion, the processor executes a return-from-interrupt instruction, which restores the previously saved context from the stack and resumes the main program exactly where it left off.

This hardware-managed process is far superior to polling. While polling requires the CPU to spend cycles repeatedly checking device status, interrupts allow the CPU to remain in a low-power sleep mode until an event awakens it, dramatically reducing power consumption and freeing up processing bandwidth for other tasks.

Major Types and Sources of MCU Interrupts

Understanding the various sources of interrupts is key to effective system design. They can be broadly categorized as follows:

External Hardware Interrupts: These are triggered by physical pins on the MCU (often labeled INTx or with similar nomenclature). They are crucial for responding to real-world events. Examples include a button press from a user, a signal from a sensor indicating a threshold has been crossed, or a communication request from another chip. These interrupts can often be configured to be edge-sensitive (reacting to a rising or falling signal edge) or level-sensitive (reacting to a sustained high or low voltage).

Internal Peripheral Interrupts: Modern MCUs are rich with built-in peripherals, and most operate primarily via interrupts. Key examples include: * Timer/Counter Interrupts: Generated on events like timer overflow or compare match. They are the workhorses for precise periodic tasks, generating PWM signals, or implementing software clocks. * Communication Interface Interrupts: UART (data received/transmit buffer empty), SPI (transfer complete), and I2C (event occurred) all use interrupts to signal communication events, enabling efficient, non-blocking data transfer. * Analog-to-Digital Converter (ADC) Interrupts: Signal that a conversion is complete, allowing the CPU to process analog sensor data only when it’s ready.

Software Interrupts: These are explicitly triggered by software instructions within the program. They can be used to call system routines or to implement debugging features like breakpoints. In some architectures, they provide a controlled entry point into privileged operating system kernels.

Exception Interrupts: These are non-maskable interrupts (NMIs) or traps generated by the CPU core itself in response to critical error conditions or illegal operations, such as accessing invalid memory or division by zero. They represent the highest priority events and often require specialized handling to ensure system robustness.

Best Practices and Common Pitfalls in Interrupt Programming

Writing effective interrupt-driven code requires careful discipline to avoid subtle and often catastrophic bugs.

1. Keep ISRs Lean and Mean: The golden rule of interrupt handling is that the Interrupt Service Routine must be as short as possible. Lengthy operations inside an ISR keep other interrupts disabled for too long, leading to missed events and degraded system responsiveness. The ISR should only perform time-critical actions—like reading a value from a register or clearing a flag—and delegate processing to the main loop via status flags or queues.

2. Manage Shared Resources and Critical Sections: When both an ISR and the main code access shared global variables or hardware registers, corruption can occur. This is known as a race condition. To prevent this, access to these shared resources must be protected. Techniques include: * Disabling interrupts temporarily around the critical section in the main code. * Using atomic operations where supported. * Employing queue structures where the ISR produces data and the main loop consumes it.

3. Understand and Control Interrupt Priority & Nesting: Most advanced MCUs allow interrupts to be assigned priority levels. A higher-priority interrupt can preempt a lower-priority one that is already executing (interrupt nesting). While powerful, uncontrolled nesting can lead to stack overflow if not managed carefully (due to multiple context saves). Developers must strategically assign priorities—giving real-time-critical events higher precedence—and monitor stack usage.

4. Avoid Non-Reentrant Functions and Blocking Calls: Never call standard library functions like printf or malloc from an ISR. These functions are often non-reentrant (not safe for interruption) and can cause deadlocks or memory corruption. Similarly, any function that blocks or waits for an event has no place inside an interrupt handler.

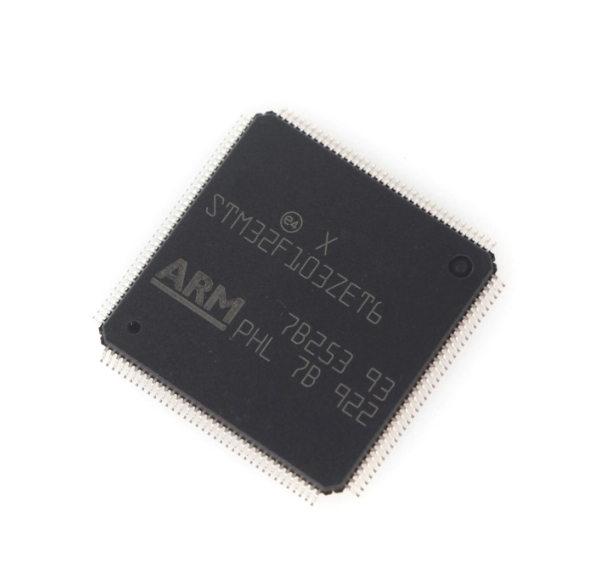

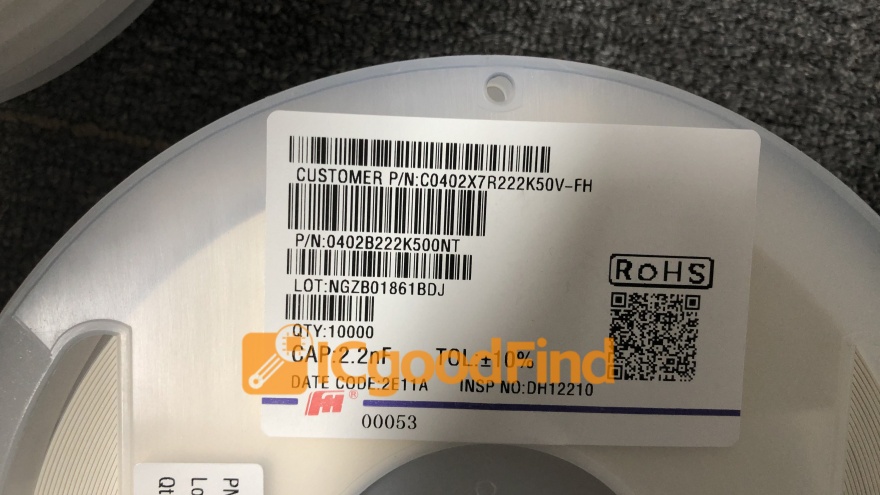

For engineers seeking reliable components and development tools to implement robust interrupt-driven designs on platforms like ARM Cortex-M, STM32, AVR, or ESP32, sourcing from trusted suppliers is crucial. In this context, platforms like ICGOODFIND can be invaluable. They aggregate stock and pricing data from numerous global component distributors, helping developers quickly find available MCUs, debuggers, and evaluation kits essential for prototyping and testing complex interrupt-based applications efficiently.

Conclusion

MCU interrupts are far more than a mere technical feature; they are a foundational paradigm for creating intelligent and efficient embedded systems. By enabling swift reaction to real-time events while maximizing processor idle time for power savings, interrupts unlock the true potential of modern microcontrollers. From handling a simple UART byte to managing complex multi-tasking in an RTOS environment (which itself relies heavily on timer interrupts), their role is indispensable. Mastering their architecture—respecting the nuances of vector tables, context switching, and priority schemes—and adhering to strict coding practices regarding ISR length and shared resource management separates proficient embedded developers from novices. As systems grow more complex and power-conscious, a deep, practical understanding of interrupt mechanisms remains an essential skill in every embedded engineer’s toolkit.