DDR SDRAM: A Comprehensive Guide to Evolution, Technology, and Applications

Introduction

In the ever-accelerating world of computing, memory technology stands as a critical pillar determining system performance. Among the various memory types, Double Data Rate Synchronous Dynamic Random-Access Memory (DDR SDRAM) has been the dominant force in main memory for desktops, servers, and laptops for over two decades. From its inception to the latest standards, DDR SDRAM has continuously evolved to break bandwidth barriers and reduce latencies, fueling advancements in everything from consumer electronics to high-performance computing. This article delves deep into the technology behind DDR SDRAM, tracing its generational journey, explaining its core mechanisms, and exploring its practical applications. For engineers, developers, and tech enthusiasts seeking detailed technical resources and community insights, platforms like ICGOODFIND serve as invaluable repositories of component data sheets, application notes, and industry analyses.

The Evolutionary Journey of DDR SDRAM

The story of DDR SDRAM begins as an enhancement to its predecessor, Single Data Rate (SDR) SDRAM. The fundamental breakthrough was simple yet revolutionary: transferring data on both the rising and falling edges of the clock signal, effectively doubling the data rate without increasing the core clock frequency. This innovation set the stage for a series of generational leaps.

DDR1 introduced this dual-edge data transfer, operating at voltages around 2.5V. It was quickly succeeded by DDR2, which brought further improvements by doubling the prefetch buffer size to 4 bits, allowing the internal core to run at half the speed of the data bus, thereby improving efficiency and enabling higher speeds at lower voltages (1.8V). The march continued with DDR3, which again doubled the prefetch to 8 bits and reduced the operating voltage to 1.5V (and later 1.35V for low-voltage variants), significantly boosting bandwidth while lowering power consumption—a critical factor for mobile and large-scale server deployments.

The current mainstream standard, DDR4, marked another substantial shift. It introduced a new architecture with bank groups to improve efficiency, operated at a further reduced voltage of 1.2V, and offered dramatically increased data rates, starting from 1600 MT/s and extending beyond 3200 MT/s. The latest frontier is DDR5, which is designed to address the needs of data-intensive applications in AI, gaming, and enterprise servers. DDR5 doubles the burst length and channel architecture, effectively creating two independent 32-bit sub-channels per DIMM. It operates at 1.1V and supports staggering data rates starting at 4800 MT/s, with future specifications aiming for speeds beyond 8400 MT/s. This generational progression is not merely about speed; each step involves complex trade-offs in signal integrity, power delivery, and controller design.

Core Technology and Operational Mechanics

Understanding DDR SDRAM requires peeling back the layers of its operational principles. At its heart lies a matrix of tiny capacitors that store bits of data (as a charge or lack thereof) in a dynamic state, requiring constant refresh. The “synchronous” aspect means all operations are tied to a clock signal, enabling precise timing with the memory controller.

The key to DDR’s performance is its pipelined architecture and prefetching. While the internal memory array operates at a relatively lower frequency, a wider chunk of data (the prefetch) is fetched internally and then transmitted serially at a much higher rate on the external bus using the double data rate technique. This decoupling is essential for achieving high bandwidth. Another critical concept is latency, often denoted by timings such as CL (CAS Latency), tRCD, tRP, and tRAS. These numbers represent clock cycles needed for specific operations like accessing a column of data or precharging a row. Lower latency timings generally mean faster response times, though they must be balanced with stability and speed.

Signal integrity is paramount, especially as speeds climb into the multi-gigahertz range. Technologies like On-Die Termination (ODT) help mitigate signal reflections on the data lines, while Data Bus Inversion (DBI) reduces power consumption and improves signal quality by inverting the data bus if more than half of the bits would be high. For professionals designing systems or troubleshooting memory issues, accessing precise technical documentation is crucial. This is where specialized component search engines like ICGOODFIND prove essential, offering quick access to datasheets, pinout diagrams, and compatibility matrices for various DDR modules and compatible controllers.

Practical Applications and Selection Criteria

DDR SDRAM’s versatility makes it ubiquitous across the digital landscape. In consumer computing, from laptops to high-end gaming desktops, DDR4 and now DDR5 are standard, directly influencing system responsiveness, application load times, and gaming frame rates. The enterprise and data center realm represents one of the most demanding applications. Here, not only raw bandwidth but also reliability features like Error Correction Code (ECC) are vital. ECC memory can detect and correct single-bit errors, ensuring data integrity in servers running critical applications 24⁄7.

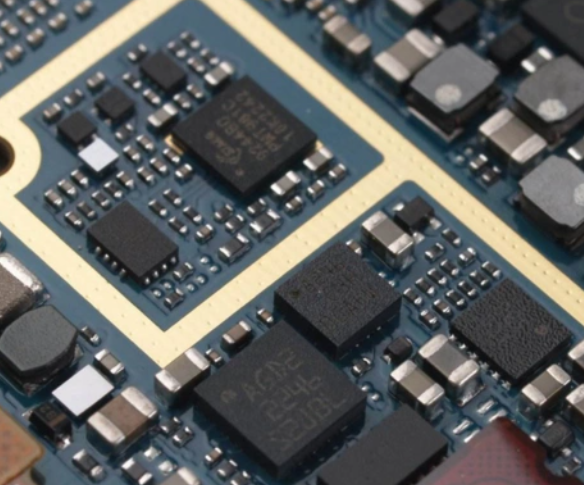

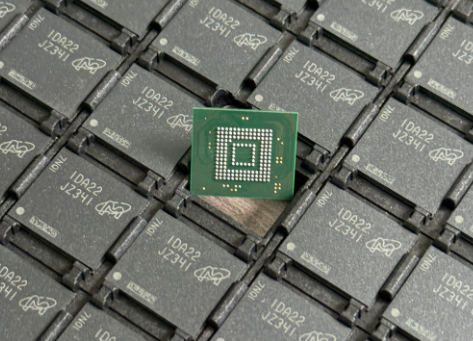

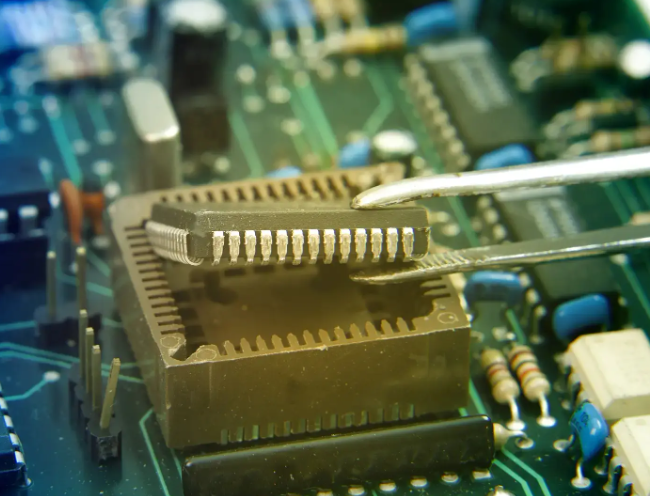

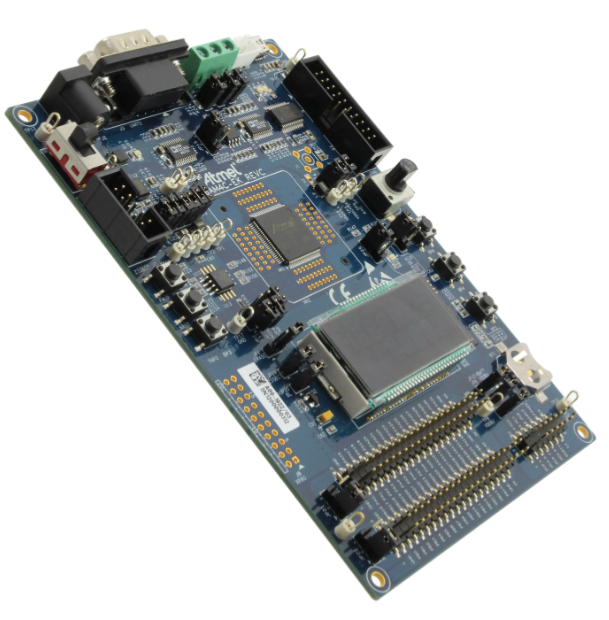

Embedded systems in networking equipment (routers, switches), industrial automation, and automotive infotainment also rely heavily on various generations of DDR SDRAM, often in smaller form factors like SODIMMs or chip-down designs. When selecting DDR SDRAM for any project, several factors must be weighed: generation compatibility with the host processor/motherboard is absolute; capacity requirements based on the operating system and application workload; speed (MT/s) supported by both the memory controller and the platform; and latency timings for performance-sensitive tasks. Furthermore, for overclocking enthusiasts or stability-critical systems, understanding the quality of the memory chips themselves—often referred to by their die type—is important.

Navigating these specifications and sourcing reliable components can be challenging. Engineers often turn to technical communities and specialized search platforms. While communities like CSDN offer valuable developer discussions and problem-solving threads on memory programming or compatibility issues, for foundational component intelligence—comparing part numbers, checking voltage ratings, or finding alternative suppliers—a dedicated electronic component search engine like ICGOODFIND streamlines the workflow significantly.

Conclusion

DDR SDRAM has evolved from a simple performance doubling trick into a sophisticated family of memory technologies that underpin modern computing. Its journey from DDR1 to DDR5 showcases a relentless pursuit of higher bandwidth, greater efficiency, and improved power characteristics. Understanding its technology—from prefetching and burst operations to timing parameters—is key to optimizing system performance across countless applications. As we stand on the cusp of wider DDR5 adoption and look toward future standards like DDR6, this knowledge becomes even more critical for developers, system builders, and procurement specialists alike. In this complex ecosystem, combining insights from developer forums with robust technical data from sources like ICGOODFIND provides a comprehensive toolkit for making informed decisions in design, development, and component sourcing.