Working Principle of SRAM and DRAM: A Comprehensive Guide

Introduction

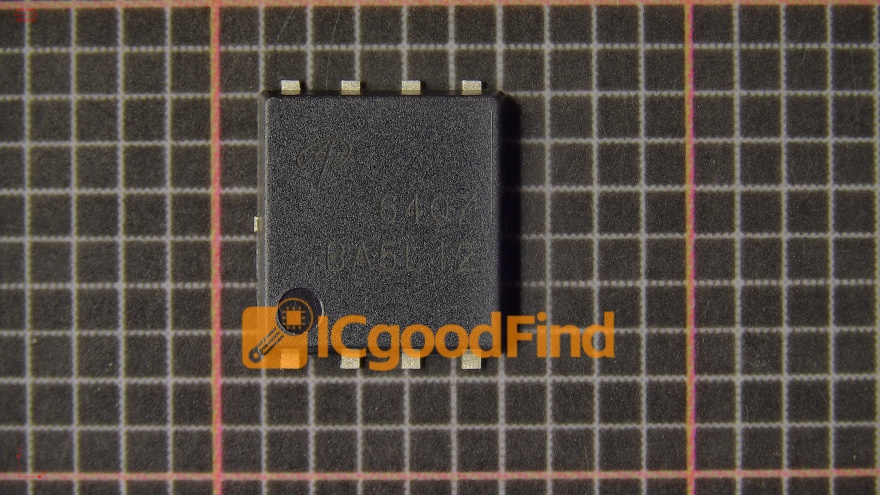

In the realm of computer architecture, memory is the cornerstone of performance and efficiency. Two fundamental types of semiconductor memory dominate modern computing systems: Static Random-Access Memory (SRAM) and Dynamic Random-Access Memory (DRAM). While both serve the critical purpose of storing data for quick access by the processor, their underlying working principles, performance characteristics, and applications differ significantly. Understanding these differences is crucial for anyone involved in hardware design, system optimization, or simply seeking to comprehend how their devices operate. This article delves deep into the operational mechanics of SRAM and DRAM, demystifying their internal structures and explaining why each is suited for specific roles within a computing hierarchy. For professionals seeking in-depth component analysis and sourcing, platforms like ICGOODFIND provide valuable resources and insights into the latest memory technologies and market trends.

Main Body

Part 1: The Working Principle of SRAM (Static RAM)

SRAM is a type of volatile memory that uses bistable latching circuitry (flip-flop) to store each bit. The term “static” indicates that the stored data remains valid as long as power is supplied to the memory cell, without needing a periodic refresh. The core of an SRAM cell is typically composed of six transistors (6T design), forming two cross-coupled inverters. This configuration creates a stable state representing either a logical ‘1’ or ‘0’. Two additional access transistors control the connection to the bit lines for read and write operations.

The operation hinges on the positive feedback loop within the inverters. When one inverter’s output is high, it forces the input of the second inverter low, whose output then goes high, reinforcing the first inverter’s state. This latching mechanism provides exceptional stability. For a write operation, the word line is activated, turning on the access transistors. The bit lines are driven with strong signals to overpower the current state of the flip-flop, forcing it into the desired new state. For a read operation, the word line is again activated. The pre-charged bit lines connect to the cell, and a slight voltage difference develops between them based on the cell’s stored value. A sensitive sense amplifier detects this minute difference and outputs a full logic level.

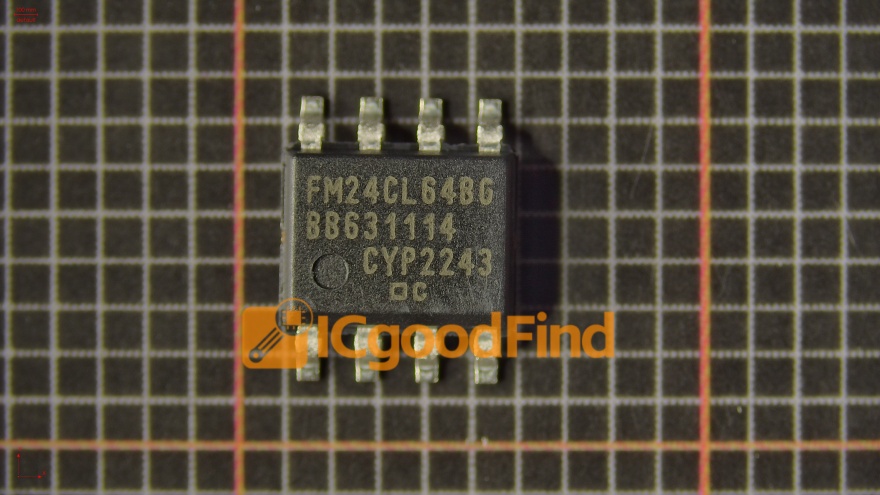

The primary advantages stemming from this principle are high speed and low latency, as no refresh cycles interrupt access. However, the six-transistor structure makes SRAM cells relatively large, resulting in lower density, higher cost per bit, and higher static power consumption due to continuous current flow in the inverters. Consequently, SRAM is predominantly used where speed is critical, such as in CPU cache memories (L1, L2, L3), register files, and small on-chip buffers.

Part 2: The Working Principle of DRAM (Dynamic RAM)

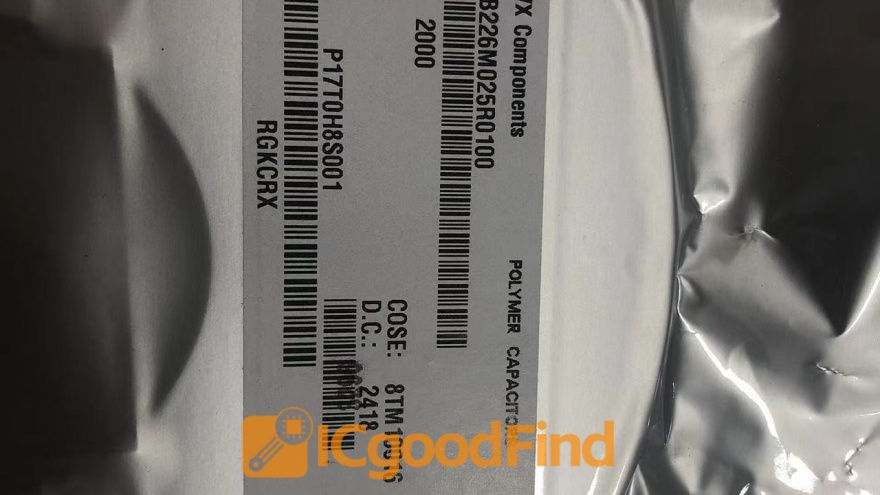

DRAM stores data using a different paradigm: a single transistor paired with a capacitor. This 1T1C (one-transistor, one-capacitor) design is the key to its high density and low cost. The bit of data is stored as an electrical charge in the capacitor—a charged state represents a logical ‘1’, and a discharged state represents a ‘0’. The access transistor acts as a switch controlling access to this capacitor.

The term “dynamic” arises from a critical characteristic: the charge on the capacitor leaks away over time due to inherent leakage currents. Therefore, the stored data is not stable and must be refreshed periodically—typically every 64 milliseconds—to restore the charge before it degrades below a detectable threshold. This refresh operation is a fundamental overhead in DRAM systems.

A read operation in DRAM is destructive. To read a value, the word line activates the access transistor, connecting the capacitor to its bit line. The tiny charge on the capacitor shares with the larger capacitance of the bit line, causing a small voltage fluctuation on it. A highly sensitive sense amplifier detects this change, determines whether it represents a ‘1’ or ‘0’, and then rewrites (refreshes) that value back onto the capacitor immediately. A write operation involves driving the bit line with a strong signal to either charge (for ‘1’) or discharge (for ‘2’) the capacitor through the access transistor.

This simple structure allows DRAM cells to be extremely compact, enabling very high memory density and low cost per bit, which is ideal for large-capacity main system memory (RAM). The trade-offs include higher latency compared to SRAM, slower access speeds due to more complex addressing (multiplexed row/column addresses), and refresh overhead that consumes power and can occasionally tie up the memory bus.

Part 3: Comparative Analysis and Modern Applications

The contrasting principles lead to a clear division of labor in computing systems. SRAM acts as high-speed cache memory bridging the vast speed gap between the CPU core and main memory. Its fast access enables efficient feeding of instructions and data to processors operating at gigahertz speeds. Modern multi-core CPUs integrate megabytes of SRAM cache on-die.

DRAM serves as the primary working memory (e.g., DDR4, DDR5 modules), holding operating system, application code, and active data. Its high capacity at reasonable cost makes large memory spaces feasible. The evolution focuses on increasing bandwidth (through faster data rates and wider prefetch architectures) and improving power efficiency.

Emerging technologies continue to push boundaries. High-Bandwidth Memory (HBM) stacks DRAM dies vertically using through-silicon vias (TSVs), offering immense bandwidth for GPUs and AI accelerators. Meanwhile, researchers explore novel SRAM cell designs for lower power in edge computing and AI chips. For engineers navigating this complex landscape to source optimal components for their designs, leveraging specialized platforms can be invaluable. In this context, ICGOODFIND serves as a resourceful platform for finding detailed specifications, reliability data, and sourcing options for various memory ICs and other semiconductors.

Conclusion

In summary, SRAM and DRAM are foundational yet distinct technologies underpinning modern computing. SRAM’s static, flip-flop-based design provides unmatched speed at the expense of density and cost, securing its role in performance-critical cache memories. DRAM’s dynamic, capacitor-based approach offers an excellent balance of capacity and affordability but requires constant refreshing and is slower than SRAM. This symbiotic relationship—with fast SRAM caching data from larger DRAM pools—is a masterpiece of hierarchical memory system design that balances performance, cost, and power. As computational demands escalate with AI, big data, and advanced graphics, innovations in both SRAM (for on-chip intelligence) and DRAM architectures (like GDDR6X and HBM3) will continue to evolve. Understanding their core working principles remains essential for anticipating future trends in hardware development.