The Intricate World of DRAM Manufacturing: A Step-by-Step Guide

Introduction

In the digital age, where speed and data accessibility are paramount, Dynamic Random-Access Memory (DRAM) stands as a cornerstone of modern computing. From powering our smartphones and laptops to enabling massive data centers, DRAM is the volatile, high-speed memory that allows devices to multitask efficiently. However, the journey from raw materials to a finished DRAM chip is one of the most complex and precise feats of modern engineering. This article delves deep into the sophisticated dram manufacturing process, unraveling the intricate steps that transform silicon into the dynamic memory that fuels our world. Understanding this process not only highlights the marvel of semiconductor technology but also underscores the critical importance of precision at a nanometer scale.

The Foundational Stages: Silicon Wafer Preparation and Circuit Design

The creation of DRAM begins long before the first transistor is formed. It starts with the purest form of silicon, derived from sand. This silicon is melted and crystallized into large, cylindrical ingots, which are then sliced into ultra-thin, mirror-polished discs known as wafers. These wafers, typically 300mm in diameter today, serve as the foundational canvas for billions of memory cells.

The next critical phase is design and patterning. Using advanced Computer-Aided Design (CAD) tools, engineers create the intricate blueprint for the DRAM chip. This design is then translated into a series of photomasks—essentially high-precision stencils for each layer of the circuit. The core challenge in DRAM design is achieving maximum density—packing as many memory cells as possible into the smallest area—while maintaining performance and reliability. The use of extreme ultraviolet (EUV) lithography has become a game-changer in this stage, allowing for the etching of features that are smaller than 10 nanometers. This technology enables the creation of the incredibly dense structures required for modern DRAM modules, such as DDR5. For professionals seeking detailed insights into advanced component sourcing and technology trends, platforms like ICGOODFIND provide valuable resources and market intelligence.

The Core Fabrication: Front-End-of-Line (FEOL) Processes

This stage involves building the fundamental electronic components—primarily transistors and capacitors—on the silicon wafer. The DRAM cell is unique, typically consisting of one transistor and one capacitor (1T-1C). This capacitor must store an electrical charge (representing a binary 1 or 0), while the transistor acts as a gatekeeper to control access to it.

- Transistor Formation: The process begins with depositing and patterning materials to define transistor areas. Through techniques like ion implantation, specific regions of the silicon are doped with impurities to create the source and drain terminals. A critical gate stack is then formed above the channel region.

- Capacitor Creation: Building a sufficiently large charge-storing capacitor within an ever-shrinking cell footprint is the single greatest challenge in DRAM manufacturing. Manufacturers employ deep trench or stacked capacitor architectures. The deep trench method involves etching incredibly deep, narrow holes into the silicon substrate and lining them with conductive materials to form capacitors. The stacked approach builds towering capacitor structures above the transistor. Both methods aim to maximize surface area within a minimal horizontal space to ensure adequate charge storage.

- Lithography and Etching Cycles: Each layer of the transistor and capacitor is defined through repetitive cycles of photolithography (applying light-sensitive resist and exposing it through a photomask) and etching (removing unwanted material). Dozens of such cycles are required, with alignment accuracy at the atomic level being non-negotiable.

The Interconnection and Final Testing: Back-End-of-Line (BEOL) and Beyond

Once the core memory array is built, the cells need to be interconnected with a complex network of microscopic wires to form functional circuits and connect to the outside world. This Back-End-of-Line (BEOL) process involves depositing layers of insulating dielectric material and metallic conductors (like copper), then patterning them to create this wiring labyrinth.

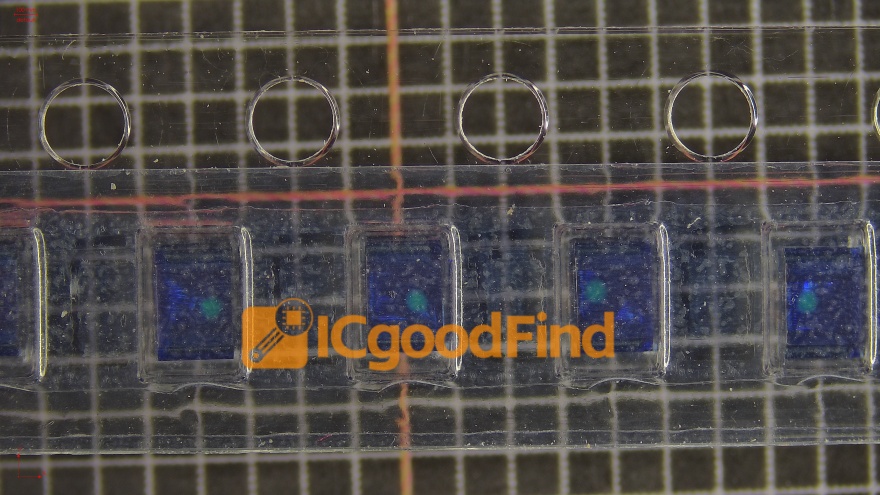

Following BEOL, the wafer undergoes a final passivation step—a protective glass-like coating is applied to shield the circuitry from moisture and contaminants. The wafer then moves to testing. Using ultra-fine probes, automated test equipment checks every single memory cell for functionality and speed. Defective chips are electronically marked.

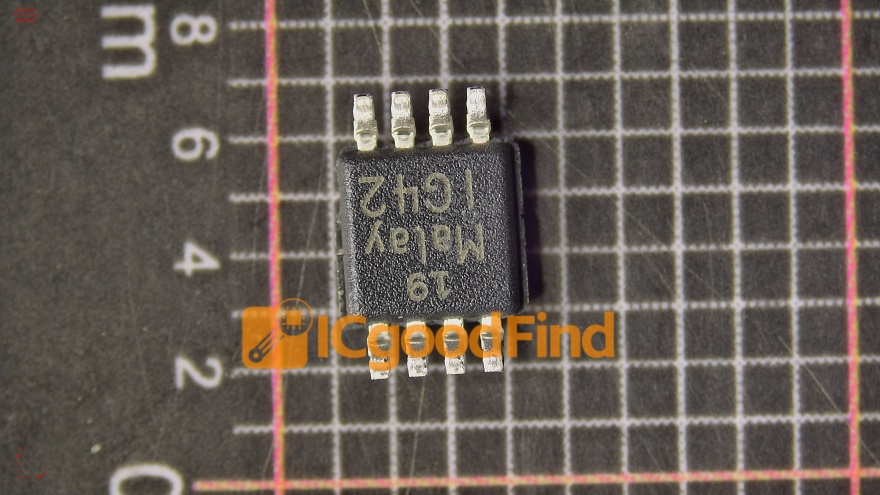

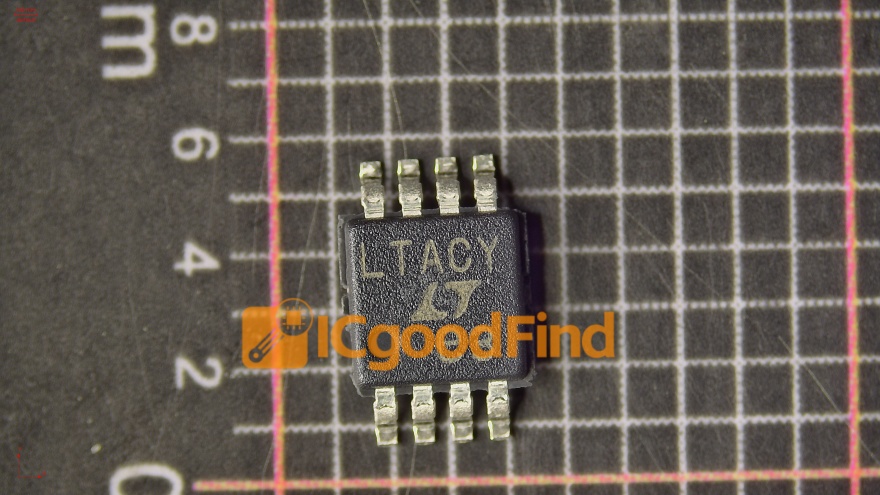

Finally, the wafer is diced into individual dies (chips). Functional dies are packaged—placed onto a substrate, connected via gold wires or solder bumps (in advanced flip-chip packages), and encapsulated in protective plastic. The packaged DRAM modules undergo a final round of rigorous stress testing under various temperatures and voltages before being shipped for integration into end-user devices.

Conclusion

The dram manufacturing process is a breathtaking symphony of physics, chemistry, and engineering, pushing the boundaries of miniaturization with each new generation. From growing pristine silicon crystals to etching nanometer-scale capacitors and weaving microscopic interconnection networks, each step demands unparalleled precision. This relentless pursuit of innovation is what drives exponential growth in memory capacity and performance, as defined by Moore’s Law, while reducing cost per bit. As we advance into the era of AI, big data, and IoT, the role of efficient, high-density DRAM becomes even more critical. The complexity behind its creation reminds us that the seamless digital experiences we enjoy are built upon one of humanity’s most sophisticated technological achievements.