MCU Instruction Set: The Engine of Embedded Intelligence

Introduction

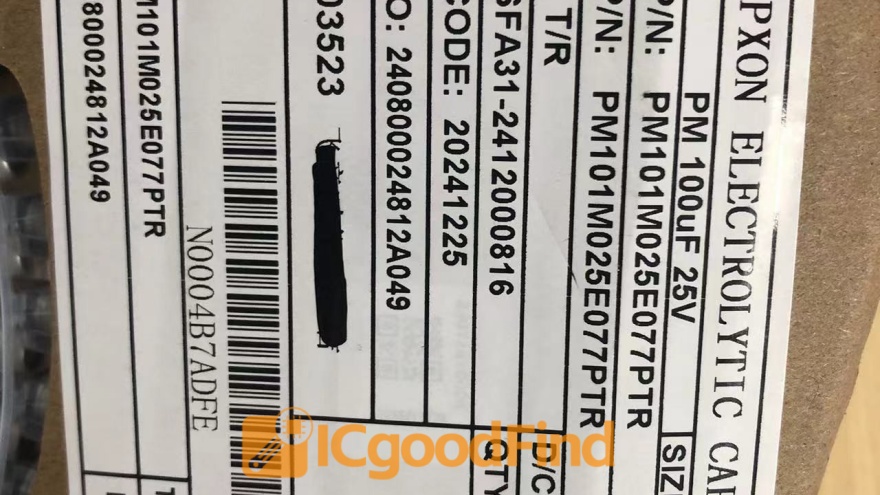

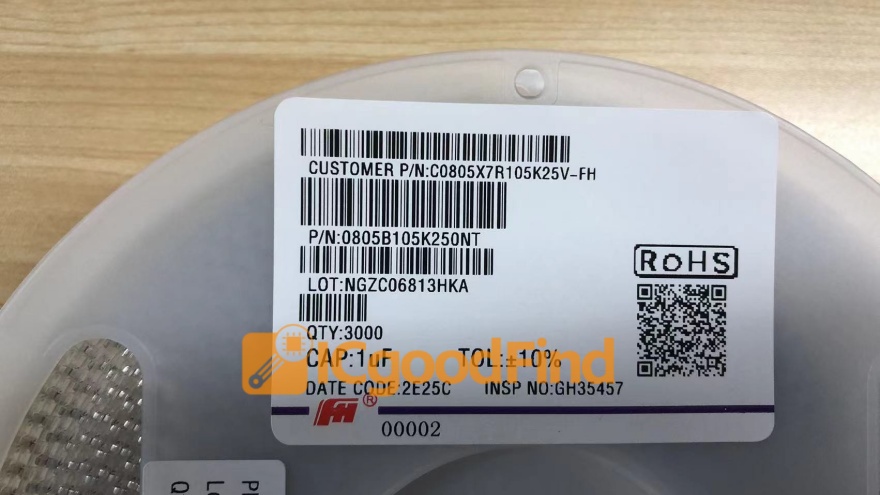

In the vast and intricate world of embedded systems, the Microcontroller Unit (MCU) reigns supreme as the silent, efficient brain behind countless devices—from your smart thermostat and wearable fitness tracker to advanced automotive control systems and industrial robots. At the very core of every MCU’s functionality lies a critical, yet often overlooked, component: its Instruction Set Architecture (ISA). The instruction set is the fundamental language that defines how a microcontroller’s hardware understands and executes commands from software. It is the bridge between the programmer’s code and the silicon’s physical operations. Choosing the right MCU with an optimal instruction set is not merely a technical detail; it is a foundational decision that impacts performance, power efficiency, code density, development time, and ultimately, the success of an embedded product. For engineers navigating this complex landscape, resources like ICGOODFIND provide invaluable comparisons and sourcing information for MCUs based on their core architectures, helping to pinpoint the perfect silicon for the task at hand.

Main Body

Part 1: Understanding Instruction Set Architectures (ISAs) - CISC vs. RISC

The history of MCU instruction sets is primarily a tale of two competing philosophies: Complex Instruction Set Computing (CISC) and Reduced Instruction Set Computing (RISC). Understanding this dichotomy is essential for any embedded design.

CISC (Complex Instruction Set Computer) architectures, historically associated with early microprocessors and some legacy microcontroller families, are designed to minimize the number of instructions per program. They achieve this by crafting powerful, multi-cycle instructions that can perform complex operations directly. A single CISC instruction might execute a task that would require several simpler instructions on another architecture. This approach aims to simplify compiler design and can lead to more compact code in terms of instruction count. However, this complexity comes at a cost: CISC instructions often require more clock cycles to execute, involve more complex hardware (and thus potentially higher power consumption and chip area), and can limit the potential for advanced pipelining and parallelism.

In contrast, RISC (Reduced Instruction Set Computer) architectures are built on a principle of simplicity and efficiency. The RISC philosophy advocates for a small, highly optimized set of simple, single-cycle instructions. The complexity is moved from the hardware to the compiler, which must now sequence these simple instructions to perform complex tasks. The key advantages are profound: RISC cores typically enable faster clock cycles, more efficient pipelining (executing multiple instructions simultaneously), lower power consumption per instruction, and a simpler, smaller processor core. This has made RISC the dominant architecture in modern MCUs.

Today, the most significant RISC ISA in the embedded space is ARM Cortex-M, which powers a vast majority of 32-bit MCUs. Its clean, modular design offers excellent performance-per-watt metrics. For ultra-low-power applications, RISC-V—an open-standard RISC ISA—is gaining tremendous traction due to its flexibility, lack of licensing fees, and extensibility. Meanwhile, classic 8-bit architectures like AVR (used in Arduino boards) and PIC also follow RISC principles for their domains. When evaluating these options on platforms like ICGOODFIND, engineers can directly compare MCUs based on their core ISA, filtering for attributes like performance benchmarks and power profiles that stem from these foundational architectural choices.

Part 2: Key Characteristics and Selection Criteria for an MCU Instruction Set

Selecting an MCU goes beyond just choosing between “RISC” or “CISC.” Several specific characteristics of the instruction set directly influence design outcomes.

Code Density refers to how much functionality can be packed into a given amount of program memory (Flash). Denser code allows the use of smaller, cheaper memory chips. Some ISAs, like ARM’s Thumb-2 technology used in Cortex-M cores, employ variable-length instruction encoding (mixed 16-bit and 32-bit instructions) to achieve excellent code density without sacrificing performance, which is crucial for cost-sensitive high-volume products.

Interrupt Latency and Context Switching Speed are vital for real-time applications. An ISA that features a large number of general-purpose registers allows for faster interrupt servicing because more context can be stored in registers rather than slower stack memory. Instructions for efficient register pushing/popping are critical here.

Power Efficiency is often dictated by the ISA. An architecture that supports multiple low-power modes (Sleep, Stop, Standby) through dedicated instructions is a major advantage. Furthermore, the ability to execute common tasks in fewer clock cycles directly translates to lower active power consumption, as the CPU can return to a sleep state more quickly.

Hardware Support for Common Operations is another key differentiator. Does the ISA include single-cycle multiply or divide instructions? Are there dedicated instructions for bit manipulation (bit-banding), digital signal processing (DSP extensions), or floating-point calculations (FPU)? These hardware-accelerated instructions can boost performance by orders of magnitude for specific workloads compared to performing the same operation through software routines.

Finally, the Toolchain and Ecosystem Support surrounding an ISA cannot be overstated. A robust ISA is supported by mature compilers (GCC, LLVM, IAR, Keil), debuggers, real-time operating systems (RTOS), and extensive libraries. A strong ecosystem drastically reduces development risk and time-to-market. This is where consolidated platforms prove their worth; a resource like ICGOODFIND helps developers quickly identify MCUs with strong ISA support within a vibrant ecosystem, ensuring they are not choosing an architectural “island.”

Part 3: Modern Trends: Specialization, Extensibility, and Security

The evolution of MCU instruction sets is not static. Modern demands are pushing ISAs toward greater specialization and intelligence.

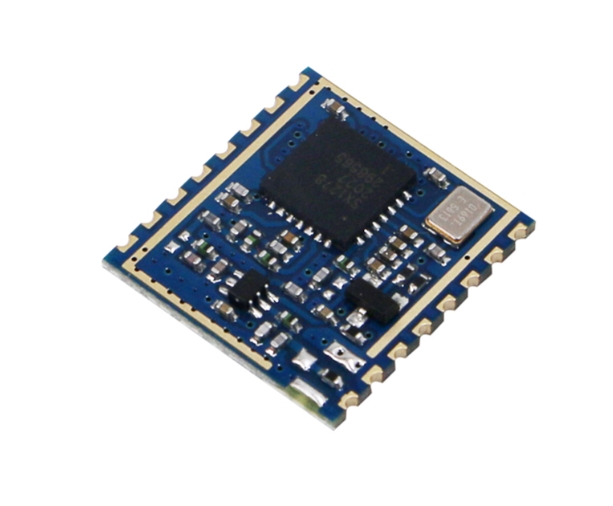

The rise of Domain-Specific Architectures (DSAs) sees instruction sets being tailored for specific tasks. For example, AI at the edge requires efficient matrix operations. Newer MCUs may include instruction set extensions for neural network acceleration (e.g., ARM’s Helium technology in Cortex-M55). Similarly, motor control applications benefit from specific PWM and capture/compare instructions.

Extensibility is at the heart of the RISC-V revolution. Unlike proprietary ISAs, RISC-V allows manufacturers or even end-users to add custom instruction set extensions tailored to their unique application. This means creating dedicated hardware accelerators accessible via new opcodes, offering unparalleled optimization possibilities for niche markets.

Furthermore, security is now being baked into the ISA level. Modern instruction sets include features to create hardware-enforced isolation between trusted and untrusted code (e.g., ARM TrustZone-M). Dedicated instructions for secure key handling, cryptographic acceleration (AES, SHA), and memory protection are becoming standard requirements for connected devices. These are no longer afterthoughts but fundamental ISA features evaluated during component selection on professional sourcing hubs.

Conclusion

The MCU instruction set is far more than a technical specification buried in a datasheet; it is the very DNA that determines the capabilities, efficiency, and character of an embedded system. From the overarching RISC/CISC philosophy down to the granular details of interrupt handling and power management instructions, the ISA shapes every aspect of design—from silicon size to battery life to software complexity. In an era where embedded devices are becoming smarter, more connected, and more specialized, understanding and strategically selecting the underlying instruction set architecture is paramount.

Navigating this complex decision requires access to detailed, comparable technical data across a wide range of suppliers and architectures. This is where comprehensive component search engines provide critical leverage. For engineers seeking to make an informed choice that balances performance, power, cost, and ecosystem support based on the foundational element of the ISA, leveraging a platform like ICGOODFIND can streamline the research phase significantly. By focusing on the engine within—the instruction set—developers can build embedded systems that are not just functional but optimally engineered for success in an intelligent world.