MCU Program Architecture: The Blueprint for Embedded System Success

Introduction

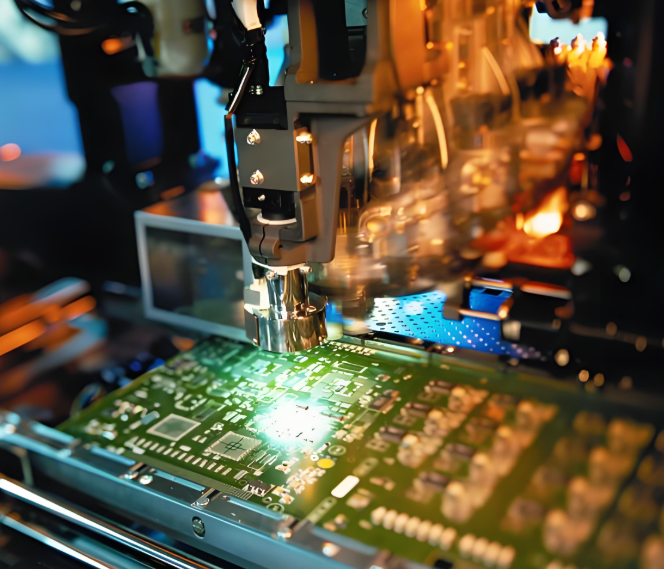

In the intricate world of embedded systems, the Microcontroller Unit (MCU) serves as the brain, but its intelligence is wholly defined by the software it executes. The architecture of this software—the MCU Program Architecture—is not merely a coding style; it is the foundational blueprint that determines a system’s reliability, scalability, performance, and long-term maintainability. As applications grow from simple blinking LEDs to complex IoT devices and automotive control systems, a well-considered program architecture transitions from a best practice to an absolute necessity. This article delves into the core principles, prevalent patterns, and critical implementation strategies that constitute robust MCU program architecture, providing a roadmap for developers to build systems that stand the test of time. For engineers seeking to deepen their practical knowledge and discover curated tools and components that align with these architectural principles, platforms like ICGOODFIND offer valuable resources to streamline the development process.

The Core Pillars of Effective MCU Program Architecture

The foundation of any strong MCU program rests on three interdependent pillars: modularity, real-time responsiveness, and resource management. Neglecting any one can lead to fragile, difficult-to-manage codebases.

Modularity and Separation of Concerns is the cornerstone. A monolithic “super-loop” where all code resides in a single endless while(1) loop quickly becomes unmanageable. The key is to decompose the system into discrete, well-defined modules based on functionality (e.g., sensor driver, communication protocol, control algorithm). Each module should have a clear interface (APIs) that hides its internal implementation details. This separation allows developers to work on individual components in isolation, dramatically simplifying testing, debugging, and future upgrades. For instance, changing a temperature sensor model should only impact its specific driver module, not the core control logic.

Real-Time Determinism and Responsiveness is non-negotiable for most embedded applications. The architecture must guarantee that critical tasks are executed within their strict deadlines. This is typically achieved through a structured approach to handling timing. The use of hardware timers and interrupt service routines (ISRs) is fundamental for time-critical event response. However, a critical architectural rule is to keep ISRs extremely short and non-blocking—they should only capture data or set flags. The actual processing should be deferred to a lower-priority task or the main loop. This prevents one interrupt from blocking others and causing missed deadlines, ensuring the system’s predictable behavior.

Efficient Resource Management is the art of optimizing within severe constraints. MCUs have limited RAM, flash memory, and CPU cycles. The architecture must explicitly account for these limits. This involves strategic decisions like using static memory allocation over dynamic (malloc/free) to avoid heap fragmentation and deterministic memory usage. It also encompasses power management at the architectural level, where modules can be put into low-power states during idle periods. A well-architected program treats resources as precious commodities, allocating them deliberately and monitoring their usage throughout the development cycle to prevent unexpected exhaustion in the field.

Prevalent Architectural Patterns for MCU Development

Moving from principles to practice, several architectural patterns have proven effective for structuring MCU software. The choice depends on the application’s complexity.

The Super Loop with State Machines pattern is an excellent starting point for moderately complex systems. While a basic super loop runs tasks sequentially, its major drawback is poor responsiveness to asynchronous events. Enhancing it with Finite State Machines (FSMs) is a transformative architectural decision. Each module or the overall application logic can be modeled as an FSM—a set of states, events, and transitions. This makes the program’s flow explicit, logical, and easy to reason about. For example, a communication protocol module (like UART command parsing) naturally fits an FSM architecture (Idle, Receiving Header, Processing Data, Sending Response). This pattern brings order to event-driven logic without the overhead of a full RTOS.

The Real-Time Operating System (RTOS) Based Architecture is the solution for complex, multi-tasking applications. An RTOS introduces concepts like tasks (threads), message queues, semaphores, and mutexes at the architectural level. It allows multiple software tasks to appear to run concurrently through preemptive or cooperative scheduling. The primary architectural benefit is the clean separation of tasks into independent execution contexts. A control task can run at 100Hz, a display update task at 10Hz, and a network monitoring task can block waiting for data—all managed efficiently by the RTOS kernel. This pattern enforces modularity and safe inter-task communication, making it ideal for systems where functionality is diverse and timing requirements are varied. However, it introduces complexity and requires careful management of stack sizes and shared resources.

Event-Driven Architecture (EDA) and Message Passing is a paradigm that promotes loose coupling between components. Instead of modules calling functions directly on each other (tight coupling), they generate and respond to events or messages placed on a queue. A sensor driver might publish a “NEW_DATA_AVAILABLE” event. A filter module subscribed to that event processes it and publishes a “FILTERED_DATA_READY” event, which a logging module then acts upon. This pattern maximizes decoupling; modules know only about the event system, not about each other. It enhances testability and allows for dynamic reconfiguration of the system’s data flow. When combined with an RTOS’s message queues or a dedicated lightweight event bus library, EDA provides a scalable and robust architectural framework.

Implementation Strategies and Best Practices

A sound architectural concept must be implemented with discipline. Here are key strategies to translate design into robust code.

Layered Architecture (HAL & Drivers) is a critical implementation strategy. Introduce a Hardware Abstraction Layer (HAL) that provides a uniform API for hardware peripherals (GPIO, SPI, I2C, ADC). The application code and upper modules interact only with the HAL, not direct register accesses. Beneath the HAL reside specific device drivers. This abstraction allows you to port your entire application to a new MCU family by primarily rewriting the HAL and drivers, leaving the high-level business logic untouched. It is a powerful investment for product longevity and code reuse.

Dependency Management and Build Systems uphold architectural boundaries at the code level. Enforce strict rules on header file inclusion to prevent circular dependencies. Use forward declarations where possible. Architect your code so that low-level drivers do not depend on high-level application logic; dependency direction should flow upward toward abstraction. Furthermore, utilize modern build systems (like CMake) or IDE project structures that visually reflect your architectural modules. This makes the architecture manifest in the file system, guiding developers and preventing accidental architectural erosion.

Testing and Debugging at an Architectural Level requires tools and approaches that align with the structure. Unit testing becomes feasible when modules are decoupled—you can test a filter algorithm by injecting mock data without needing real hardware. Integration testing can verify event flows and inter-module communication. Instrumentation through architectural trace points, such as logging state transitions or event counts to a spare UART or in-memory buffer, provides invaluable runtime insight into system behavior without halting execution (unlike breakpoints). This high-level visibility is crucial for validating that the architecture is functioning as designed in real-time.

Conclusion

Crafting a deliberate MCU Program Architecture is what separates professional, sustainable embedded systems from hobbyist projects that become unmaintainable dead-ends. It is an upfront investment that pays continuous dividends in reduced bug counts, easier team collaboration, straightforward feature integration, and enhanced product reliability. By embracing modularity with clear interfaces, selecting the appropriate architectural pattern—be it state machine-enhanced super loops, RTOS-based multitasking, or event-driven systems—and adhering to implementation best practices like HAL layering, developers construct software that is not just functional but resilient and adaptable.

The journey towards mastering MCU architecture is ongoing, fueled by both practice and access to quality resources that exemplify these principles in action. Platforms dedicated to aggregating vetted electronic components and development tools can significantly accelerate this learning curve by connecting engineers with the right building blocks for their architectural vision.