Dual-Axis Motor Control System: Hardcore Support for Safety and Efficiency

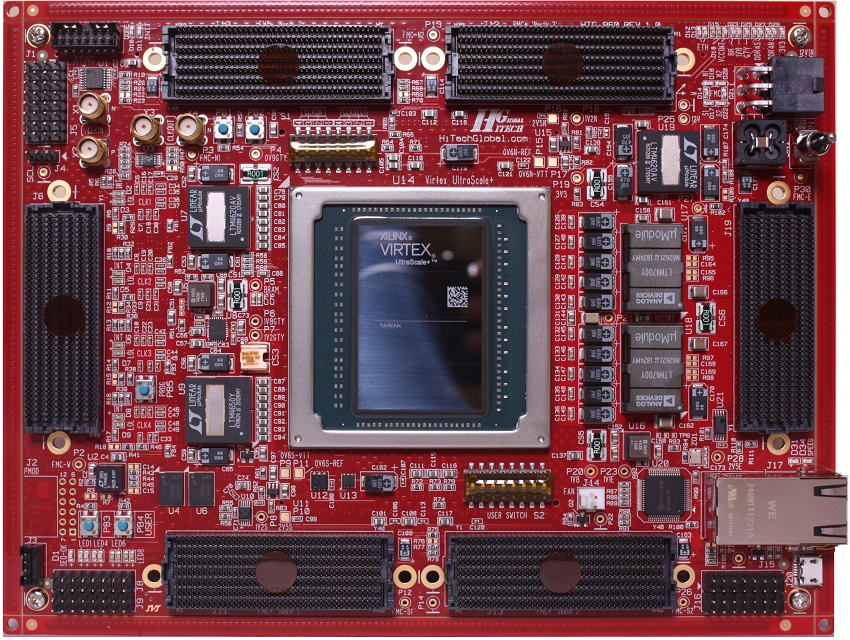

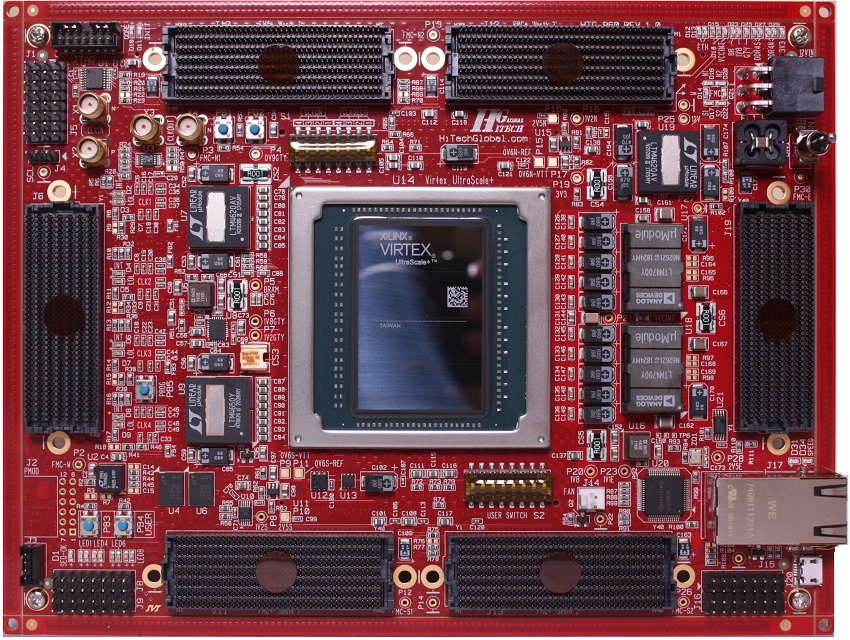

As industrial automation, robotics, and automotive systems become increasingly sophisticated, certified functional safety and real-time control performance have become indispensable requirements. The dual-axis motor control system jointly presented by Altera and MathWorks not only achieves TÜV certification at the Cat. 3 PLd safety level but also uses the Agilex™ 5 SoC FPGA as its core carrier. It skillfully integrates model-based development with a flexible, portable safety architecture, providing robust technical support for balancing safety and efficiency in industrial control.

Model-Based Design Flow

The development of this dual-axis motor control system centers on a model-based design approach:

Altera’s DSP Builder Advanced Blockset integrates directly with MATLAB and Simulink, enabling control engineers to design, simulate, and optimize algorithms at the system level. These algorithms are then automatically compiled into synthesizable RTL code, which is directly deployed to the FPGA logic structure, simplifying the process from model to hardware.

This demonstration uses a simulated industrial motor model instead of a physical motor, allowing parameterized testing under different load conditions, drive topologies, and performance targets without repeated hardware design iterations.

This method significantly shortens the development cycle, maintains high fidelity between simulation and actual hardware deployment, and supports rapid design exploration.

Dual-Channel Functional Safety Architecture: Heterogeneous Redundancy

Meanwhile, the system achieves functional safety through two independent speed monitors:

- Monitor Channel 1 runs entirely within the FPGA logic structure.

- Monitor Channel 2, implemented as software, runs on the Arm®-based hard processor subsystem (dual-core Cortex-A55, dual-core Cortex-A76 processors, and hard peripherals) integrated into the Agilex™ 5 SoC FPGA.

This monitor redundancy mechanism mitigates both systematic faults (software defects and toolchain errors) and random hardware faults (such as single-event upsets), meeting the stringent TÜV Rheinland Cat. 3 PLd certification requirements.

Through hardware-software collaboration, the system builds orthogonal safety verification paths, enhances fault tolerance, and simplifies safety documentation for industrial, automotive, and robotics applications.

Portability Across Altera FPGA Product Families

Additionally, the demonstration design offers portability:

If an application does not require the complexity and high performance of an integrated Arm processor, control and safety functions can be ported to Altera’s RISC-V-based Nios® V soft-core processor.

The Nios® V soft-core provides a flexible, lightweight alternative that maintains real-time performance while expanding the range of applicable Altera FPGA product families.

This allows the solution to adapt to multiple FPGA product lines, from low-cost edge motor controllers to complex multi-axis robotic arms, without redesigning core safety logic.

Real-Time Performance and System Responsiveness

Beyond safety, the Agilex™ 5 SoC FPGA architecture offers:

- Low-latency, deterministic control of critical paths via FPGA hardware.

- Software programmability based on Arm processors or Nios® V cores, supporting monitoring, diagnostics, and runtime updates to enhance responsiveness of field-deployed devices.

- Fine-grained motor simulation and high-speed, low-jitter signal paths, critical for robotics, servo drives, and autonomous mobile systems.

Through synchronized deterministic control and exceptional flexibility, the system better enables edge analysis and safety monitoring, achieving an optimal balance of performance, safety, and adaptability.

Simplifying Certification, Focusing on Innovation

The joint toolchain from MathWorks and Altera helps simplify:

- Algorithm design and verification via DSP Builder.

- Automatic HDL code generation via DSP Builder.

- Accelerated safety verification through TÜV-reviewed architectures and documentation.

- Faster overall functional development with Altera FPGA hardware validation.

This integrated flow shortens certification cycles, reduces development risks, and provides an efficient technical path for engineers to accelerate the launch of safety-critical innovations.