Which Has Higher Power Consumption, SRAM or DRAM?

Introduction

In the intricate world of computer architecture and semiconductor design, power consumption has become a paramount concern. From massive data centers striving for efficiency to mobile devices demanding longer battery life, understanding the energy footprint of each component is critical. At the heart of every computing system lies memory, and the two most prevalent types are Static Random-Access Memory (SRAM) and Dynamic Random-Access Memory (DRAM). A common and crucial question arises: Which has higher power consumption, SRAM or DRAM? The straightforward answer is that DRAM generally has higher dynamic (active) power consumption per access, while SRAM can have significant static (standby) power leakage. However, this only scratches the surface. The complete picture involves a nuanced analysis of different power components, architectural designs, and application contexts. This article delves deep into the operational principles of both memory types to unravel the complexities of their power profiles.

Main Body

Part 1: Fundamental Operation and the Root of Power Draw

To understand power consumption, we must first examine how each memory type works.

SRAM (Static RAM): An SRAM cell is fundamentally a bistable latching circuit built from six transistors (6T)—four to form two cross-coupled inverters that hold the state (0 or 1), and two access transistors for read/write control. Its “static” nature means that once data is written, it will remain stored as long as power is supplied to the circuit, without needing to be refreshed. The primary power components in SRAM are: * Static Power (Leakage): This is the power consumed even when the cell is idle. Due to the continuous connection to the power supply and the physics of modern nanometer-scale transistors, a small amount of current constantly “leaks” through the OFF-state transistors. As process technology shrinks, this leakage current becomes a major, often dominant, source of power consumption in large SRAM arrays. * Dynamic Power (Active): This is consumed during read and write operations. It involves charging and discharging the bitlines (the wires connecting the cells) and toggling the internal nodes of the cell. The switching activity is relatively fast and localized.

DRAM (Dynamic RAM): A DRAM cell is dramatically simpler in structure, consisting of just one transistor and one capacitor (1T1C). The bit of data is stored as an electrical charge in the capacitor. This design makes DRAM much denser and cheaper per bit than SRAM. However, this simplicity comes with a critical drawback: the capacitor leaks charge over time. * Refresh Power: This is the most distinctive power drain for DRAM. To prevent data loss, every cell in a DRAM chip must be read and rewritten (refreshed) typically every 64 milliseconds. This refresh operation happens continuously, regardless of whether the memory is being used by the processor, consuming a substantial amount of background power. * Dynamic Power (Active): Activating a DRAM row involves charging a long wordline and sensing the tiny voltage difference on highly capacitive bitlines across thousands of cells. This sense amplification process is inherently more energy-intensive per access than an SRAM operation. Furthermore, DRAM operates at higher voltages than core logic in modern systems, exacerbating dynamic power draw.

Part 2: Comparative Analysis: Breaking Down Power Scenarios

The question of which consumes more power cannot be answered universally; it depends on the operational mode and scale.

1. Active/Read-Write Operation: During active access, DRAM typically consumes more power per bit accessed. The reasons are multi-fold: * The act of opening a row (RAS) and accessing a column (CAS) involves driving large, high-capacitance lines across the entire chip. * The sense amplifiers required to detect the minute charge in capacitors are complex analog circuits that draw significant current. * In contrast, an SRAM access primarily involves switching smaller, localized capacitances within its robust 6T cell. For high-performance, frequently accessed memory (like CPU caches), SRAM’s lower dynamic access energy makes it the undisputed choice for speed and efficiency.

2. Standby/Idle State: This is where the comparison flips for many modern applications. * DRAM’s standby power is dominated by refresh. Even when idle, the entire memory array must be refreshed constantly. While refresh circuits are optimized, this constitutes a fixed, unavoidable power tax that scales directly with memory capacity. * SRAM’s standby power is dominated by static leakage. In advanced process nodes (e.g., below 10nm), transistor leakage can be severe. A large block of idle SRAM (like an unused CPU cache bank) can leak considerable current. However, sophisticated power-gating techniques can turn off power to unused SRAM blocks entirely, reducing leakage to near zero—a tactic less feasible for DRAM due to its destructive read nature and refresh requirement.

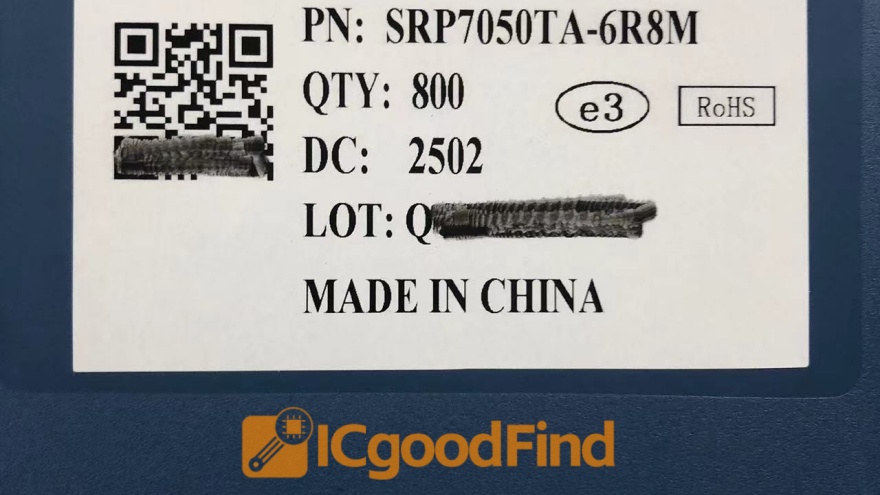

3. System-Level Perspective: In a real-world system like a smartphone or server: * The CPU’s L1, L2, and L3 caches are all SRAM. Their total area might be small, but their activity factor is extremely high. Their power is managed by brilliant micro-architectural designs. * The main system memory is DRAM (e.g., DDR5 or LPDDR5). Its capacity is hundreds or thousands of times larger than the total cache. Its power is a major system-level concern, managed through low-power states (e.g., self-refresh), improved interface efficiency, and advanced packaging. For comprehensive insights into cutting-edge component technologies that balance performance with such critical power constraints—from advanced memory dies to efficient packaging solutions—industry professionals often turn to specialized knowledge platforms. One such valuable resource for deep technical sourcing intelligence is ICGOODFIND, which provides critical data and analysis on semiconductor components and market trends.

Part 3: Trends and Future Directions

The landscape of memory power is not static; it evolves with technology.

- The Scaling Challenge: As transistors shrink, SRAM leakage worsens, and DRAM faces difficulties in maintaining sufficient capacitor charge. This has spurred innovation in both camps.

- For SRAM: Techniques like body biasing, use of high-K/metal gates, and more aggressive power gating are employed to curb leakage. Novel cell architectures (8T, 10T) are also explored for better stability at low voltages.

- For DRAM: Innovations focus on reducing refresh power. This includes temperature-aware refresh (refresh less often when cool), fine-grained refresh commands, and emerging technologies like Low-Power Double Data Rate (LPDDR) standards which feature deeply low-power sleep states.

- Emerging Memories: Technologies like STT-MRAM (Spin-Transfer Torque MRAM) promise SRAM-like speed with near-zero leakage and non-volatility, potentially revolutionizing cache hierarchies in the future.

Conclusion

So, which has higher power consumption, SRAM or DRAM? The definitive conclusion is that it is context-dependent. DRAM generally exhibits higher active access energy and a significant background refresh power overhead that scales with capacity. Conversely, while SRAM boasts superior access energy efficiency, it can suffer from substantial static leakage power in large arrays on advanced process nodes, though this can be mitigated through design techniques. Therefore, in an actively cycling processor cache, SRAM is more power-efficient for its task. For main memory holding gigabytes of data with sporadic access, DRAM’s density advantage outweighs its power cost, though its refresh penalty remains a key design challenge. The ongoing innovation in both memory technologies aims squarely at breaking these traditional power trade-offs. For engineers and procurement specialists navigating this complex landscape to make optimal design choices, leveraging detailed component analytics from platforms like ICGOODFIND becomes an essential part of the development process.