SRAM vs DRAM: Understanding the Key Differences in Computer Memory

Introduction

In the intricate architecture of modern computing, memory plays a pivotal role in determining system performance, efficiency, and capability. Two fundamental types of memory—Static Random-Access Memory (SRAM) and Dynamic Random-Access Memory (DRAM)—form the backbone of data storage and retrieval in virtually every digital device. While both serve the essential function of holding data for the processor, their underlying technologies, applications, and characteristics differ dramatically. For engineers, IT professionals, and technology enthusiasts, grasping the fundamental distinction between SRAM and DRAM is crucial for making informed decisions about hardware design, system optimization, and component selection. This article delves deep into their architectures, operational principles, and real-world applications to provide a comprehensive comparison.

Part 1: Architectural and Operational Fundamentals

At their core, SRAM and DRAM are designed using different electronic principles, which directly dictate their performance and behavior.

SRAM (Static RAM) is built using a bistable latching circuit, typically composed of four to six transistors per memory cell. This configuration creates a flip-flop circuit that can hold its state (a 0 or a 1) as long as power is supplied to the system. The term “static” refers to this ability to retain data without needing to be periodically refreshed. The data remains stable and instantly accessible. This architecture makes SRAM significantly faster, as data retrieval does not involve a refresh cycle or capacitor recharge. However, the use of multiple transistors makes the SRAM cell physically larger, more complex to manufacture, and more power-hungry in terms of static leakage current, though it consumes less power during active operation due to the absence of refresh cycles.

DRAM (Dynamic RAM), in contrast, stores each bit of data in a separate tiny capacitor within an integrated circuit. A single transistor acts as a gate, controlling whether the capacitor’s charge (representing a 1) or lack of charge (representing a 0) can be read or written. The critical challenge with DRAM is that these capacitors leak charge over time. Therefore, the data is “dynamic” and will fade unless it is periodically refreshed, typically every few milliseconds (e.g., 64ms). This refresh process involves reading the data and rewriting it back to restore the charge. While this refresh overhead introduces latency and requires constant power management, the one-transistor-one-capacitor (1T1C) design allows DRAM cells to be much smaller and simpler than SRAM cells. This translates to vastly higher density (more bits per chip) and lower cost per bit.

Part 2: Performance Characteristics: Speed, Density, and Power

The architectural differences lead to a clear trade-off triangle between speed, density/cost, and power consumption.

Speed and Latency: SRAM is unequivocally faster than DRAM. With access times typically in the low single-digit nanoseconds, SRAM’s speed stems from its direct, flip-flop-based access that doesn’t require a refresh cycle or sense amplifiers to detect minute capacitor charges. This makes it ideal for applications where speed is paramount. DRAM has higher latency, with access times generally ranging from tens to over a hundred nanoseconds. The need to activate rows of capacitors, use sense amplifiers to read the fragile charge state, and manage refresh cycles all contribute to this delay.

Density and Cost: Here, DRAM holds a decisive advantage. Its simple 1T1C structure allows for incredibly dense memory arrays. A single DRAM chip can store gigabytes of data, making it the universal choice for a system’s main memory (RAM), where large capacity is essential. SRAM is much less dense due to its multi-transistor cell. You would need a physically enormous and prohibitively expensive chip to achieve the same capacity as a standard DRAM module. Consequently, SRAM is used in smaller, critical capacities where speed outweighs cost concerns.

Power Consumption: The comparison is nuanced. SRAM consumes less dynamic power during active read/write cycles because it doesn’t require constant refreshing or charging large capacitor arrays. However, it suffers from significant static power dissipation due to continuous current flow through its transistors. DRAM consumes more active power during operations due to the energy needed to charge/discharge capacitors and run sense amplifiers. Its background refresh power is also a constant draw, even when the system is idle. However, advanced power-down modes in modern DRAM can mitigate this in low-activity states.

Part 3: Primary Applications and Market Roles

Their distinct characteristics naturally steer SRAM and DRAM toward different roles within a computing hierarchy.

SRAM Applications: Its blazing speed justifies its use in small-capacity, performance-critical caches. * CPU Caches (L1, L2, L3): This is SRAM’s most prominent application. Located directly on or very close to the processor die, these caches store frequently accessed instructions and data to feed the CPU cores at their maximum clock speeds. * Register Files: Inside the CPU core itself. * Small Embedded Systems & IoT Devices: Where very low power consumption (in active mode) and deterministic speed are needed for specific tasks. * Networking Equipment: In router buffers and look-up tables where ultra-fast access is non-negotiable.

DRAM Applications: Its high density and lower cost make it the workhorse for main system memory. * System Main Memory (RAM): In desktops, laptops, servers (as DDR4, DDR5 modules), smartphones (LPDDR), and graphics cards (GDDR). It holds the operating system, applications, and active data for quick access by the CPU via its caches. * Frame Buffers in Graphics: Though GDDR is a specialized variant optimized for bandwidth.

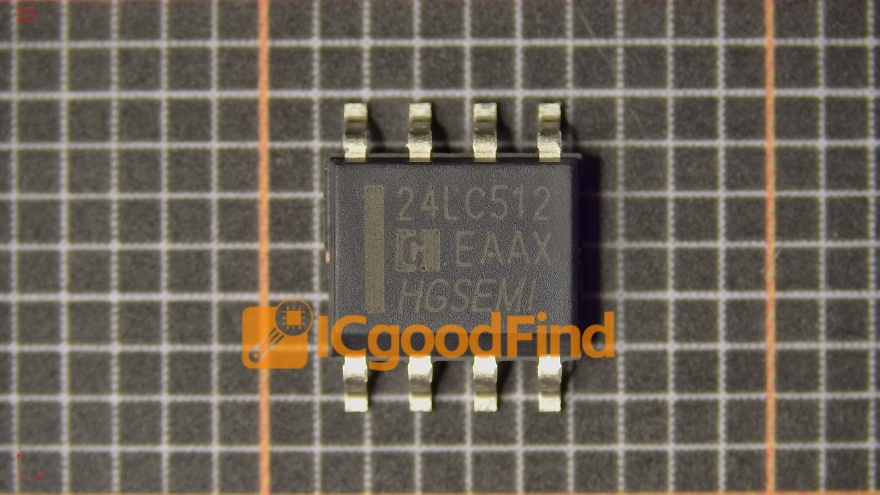

Understanding this ecosystem is vital for professionals involved in hardware specification or system tuning. For those seeking detailed technical specifications, performance benchmarks, or sourcing information for specific memory components from leading distributors across Asia—including Taiwan—a resource like ICGOODFIND can be invaluable for finding reliable component data sheets and supplier information.

Conclusion

The difference between SRAM and DRAM is not merely academic; it is a foundational design choice that shapes computing performance. SRAM offers superior speed and simpler access but at a high cost per bit and low density, reserving its place in small, critical buffers like CPU caches. DRAM provides high-density, cost-effective storage for vast amounts of data but introduces latency through its need for constant refreshing, making it perfect for expansive main memory. They are not competitors but complementary technologies working in tandem: SRAM acts as a swift staging area close to the CPU, while DRAM serves as the vast primary warehouse of active data. As computing evolves with new architectures like chiplet designs and advanced packaging (e.g., HBM stacks using DRAM), this symbiotic relationship continues to be optimized. The ongoing innovation in both memory types—from faster LPDDR5X DRAM for mobile devices to larger last-level caches using SRAM—ensures that understanding their core differences remains essential for navigating the future of technology.