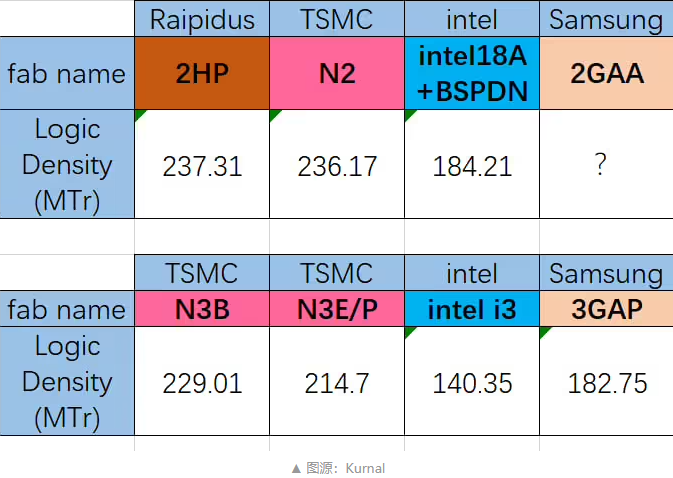

Per insider Kurnal, fitting calculations of Japanese chipmaker Rapidus’ cutting-edge 2nm 2HP node show its logic density hits 237.31 MTr/mm²—nearly identical to TSMC’s same-generation N2 (236.17 MTr/mm²). This places Rapidus among the industry’s top tier for logic density, a key chip manufacturing metric.

Notably, Intel’s 18A node uses BSPDN backside power delivery (a design-altering tech), so its logic density can’t be directly compared to non-BSPDN 2nm processes—making Rapidus’ performance here standout.

Logic density only covers the "Area" in PPA (Performance, Power, Area). To fully assess Rapidus’ 2nm process, Power (consumption) and Performance data are still needed. For commercial success, yield rate and production efficiency also remain critical.

Rapidus has advanced steadily: it trial-produced its first 2nm GAA wafer in July, with a 2027 target of 25,000 wafers per month (25,000 WPM) mass production—if met, this will boost its global chip market position.

ICgoodFind will track this fierce semiconductor process competition and share latest updates.

At ICgoodFind, we see Rapidus’ 2nm progress as a notable global semiconductor shift. We’ll keep monitoring power, yield, and more to keep you informed.